# SERVICE MANUAL

DVD HOME CINEMA SYSTEM

# CONTENTS

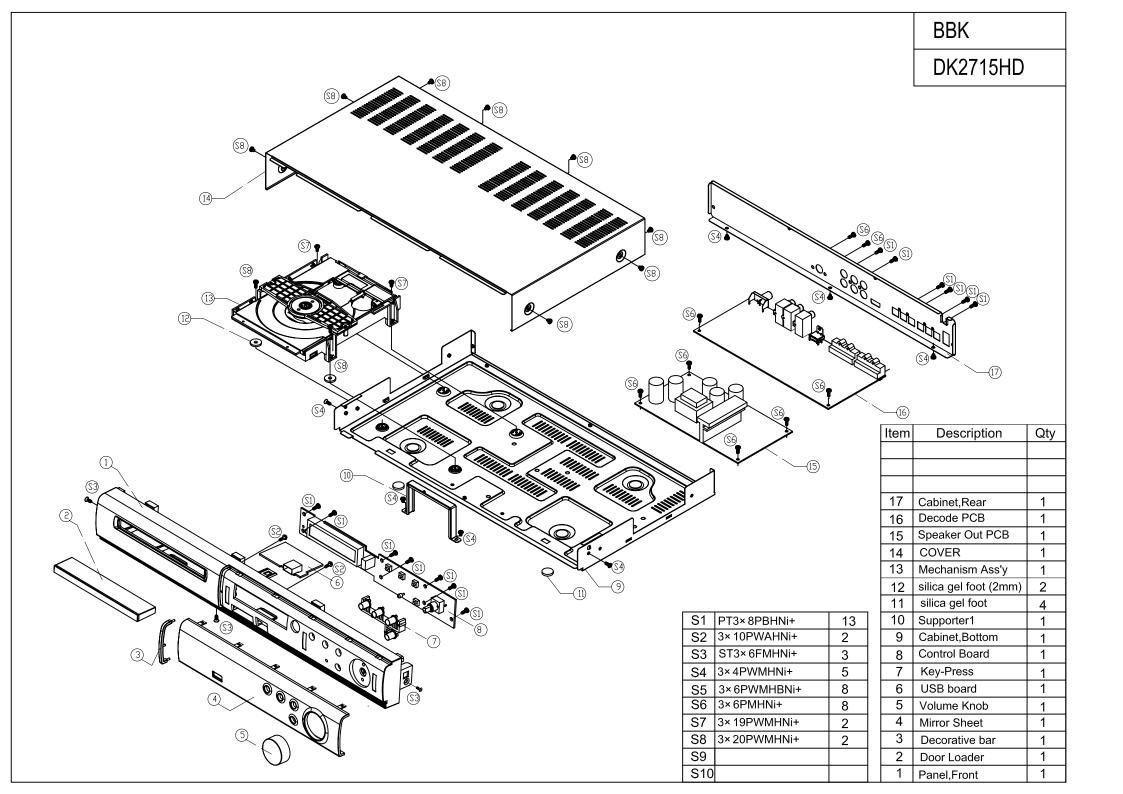

| 1. PRECAUTIONS                                         | 2       |

|--------------------------------------------------------|---------|

| 1-1 SAFETY PRECAUTIONS                                 | 3<br>3  |

| 2. REFERENCE INFORMATION                               |         |

| 2-1 Component Descriptions                             | 5       |

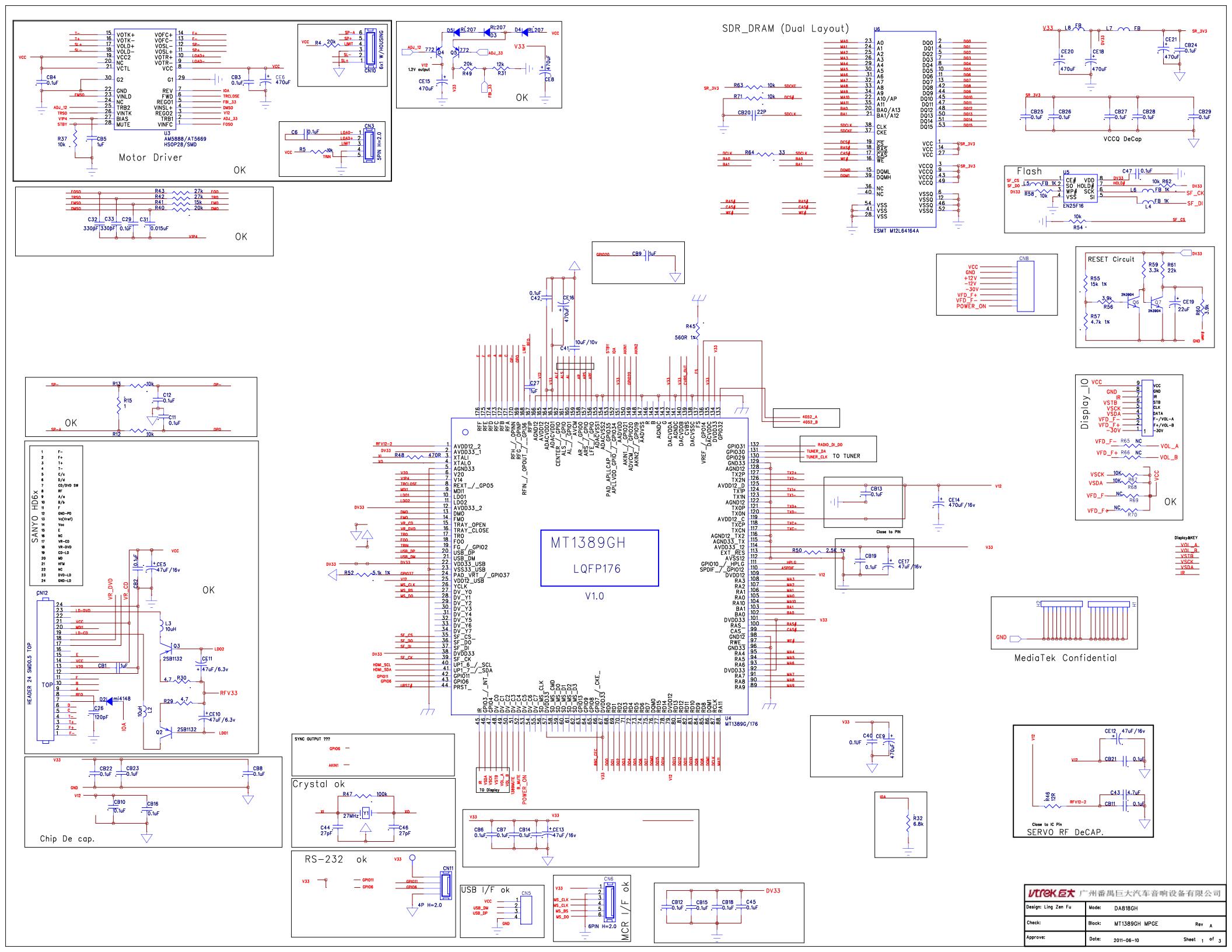

| 2-1-2 DVD Processor Chip MTK1389GH                     |         |

| 2-1-1 DVD SONY HM-313 PUH                              |         |

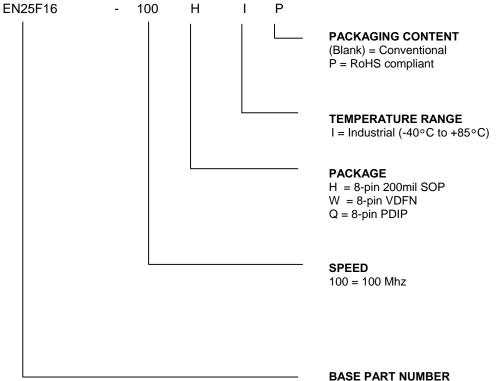

| 2-1-3: FLASH MEMORY( CMOS 16M (2M _ 8/1M _ 16) BIT)    | 52-84   |

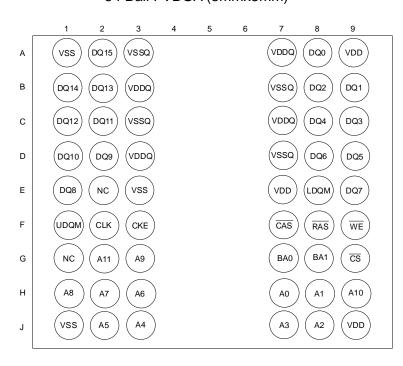

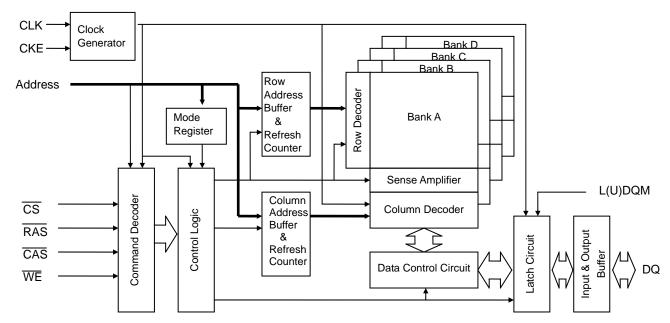

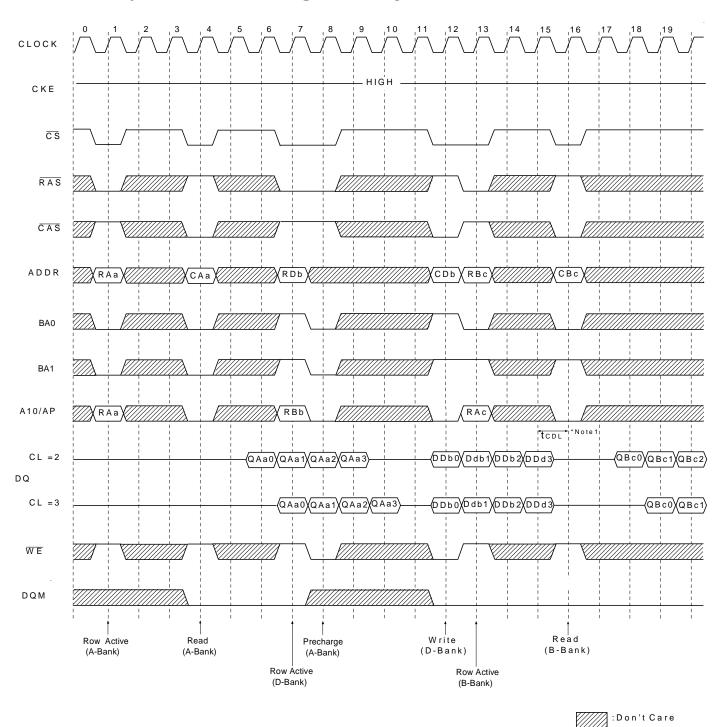

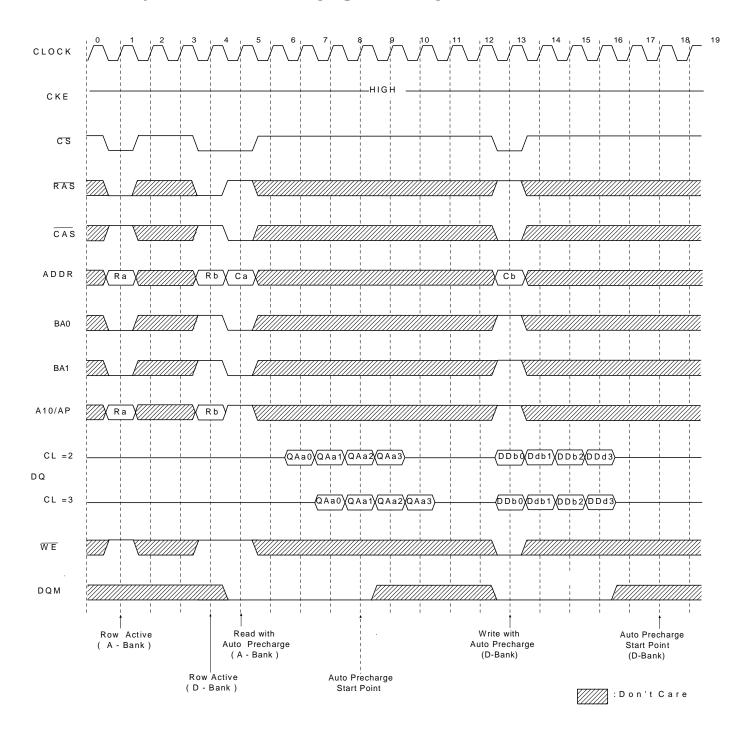

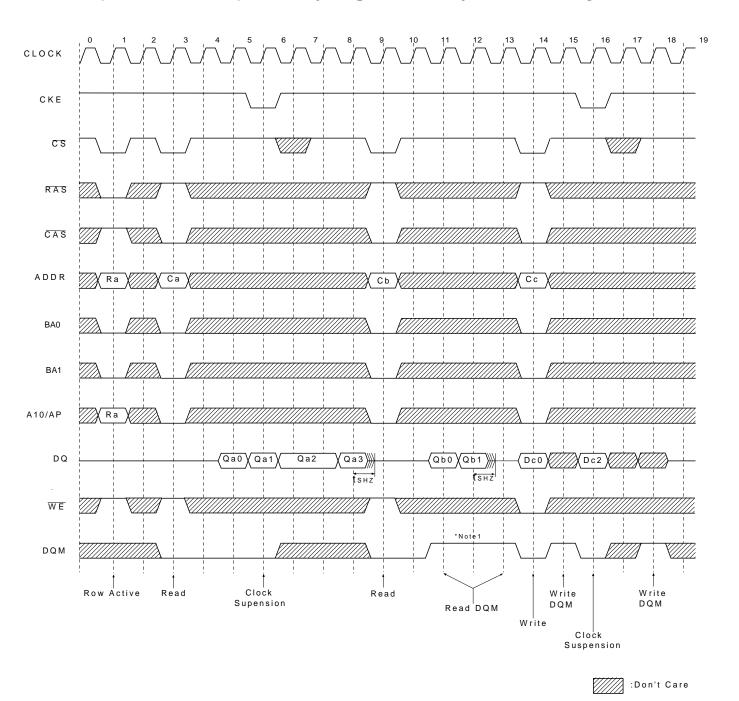

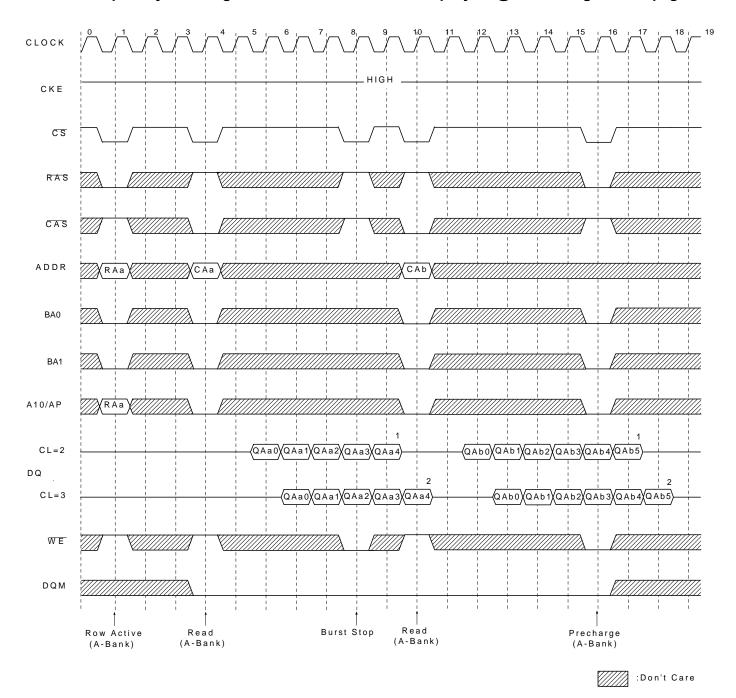

| 2-1-4 4 Banks x 1M x 16Bit Synchronous DRAM M12L64164A | 85-130  |

| 3. PRODUCT SPECIFICATIONS                              | 131     |

| 4. UPGRADING SYSTEM AND CHANGING THE REGION CODE       | 132     |

| 5. OPERATING INSTRUCTION                               | 133     |

| MAINTENANCE & TROUBLESHOOTING                          | 133     |

| 6.PROBLEMS AND SOLUTIONS                               | 134     |

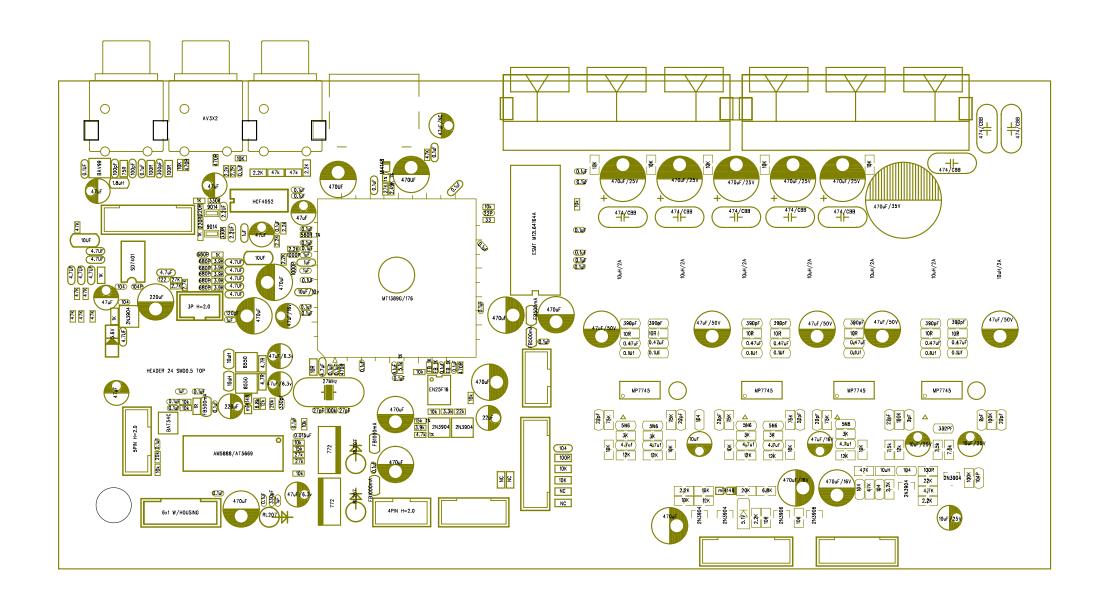

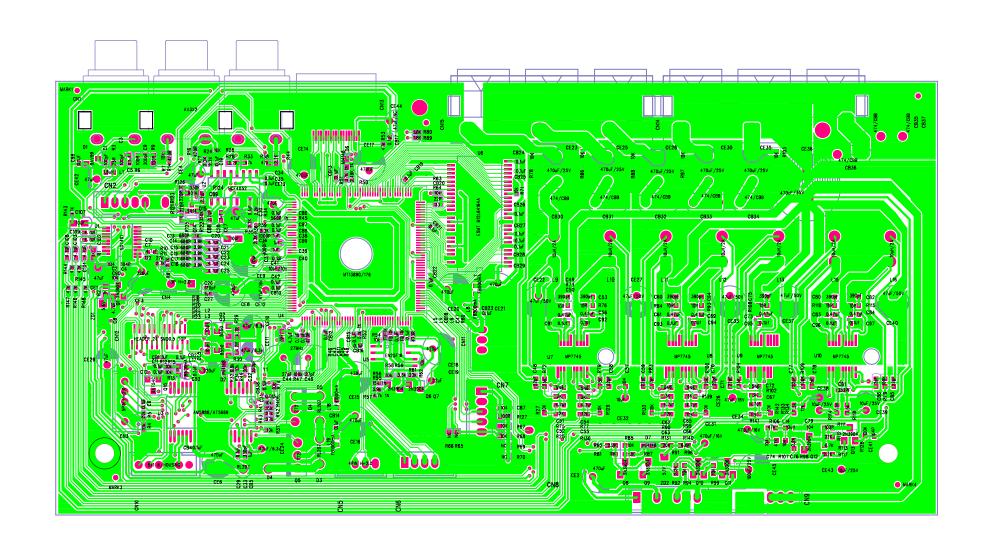

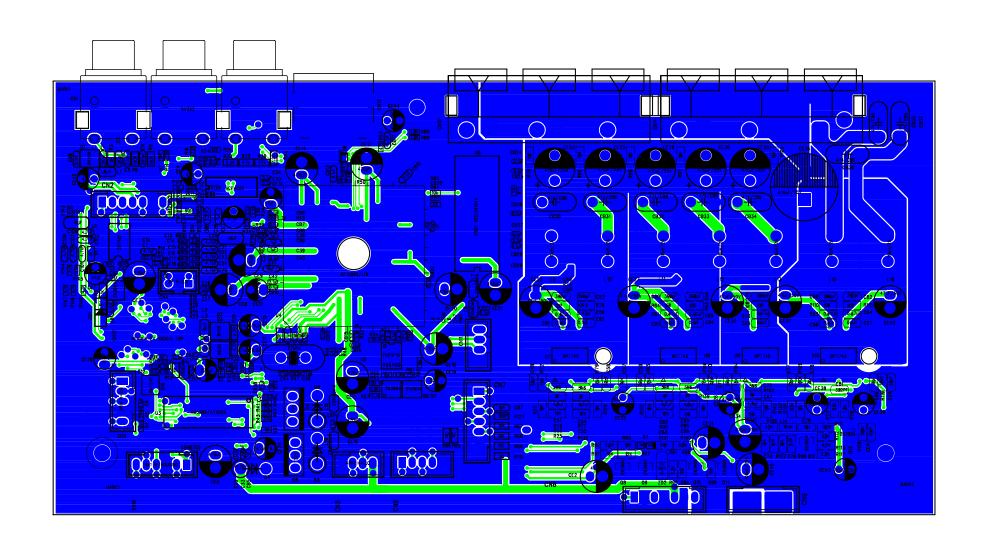

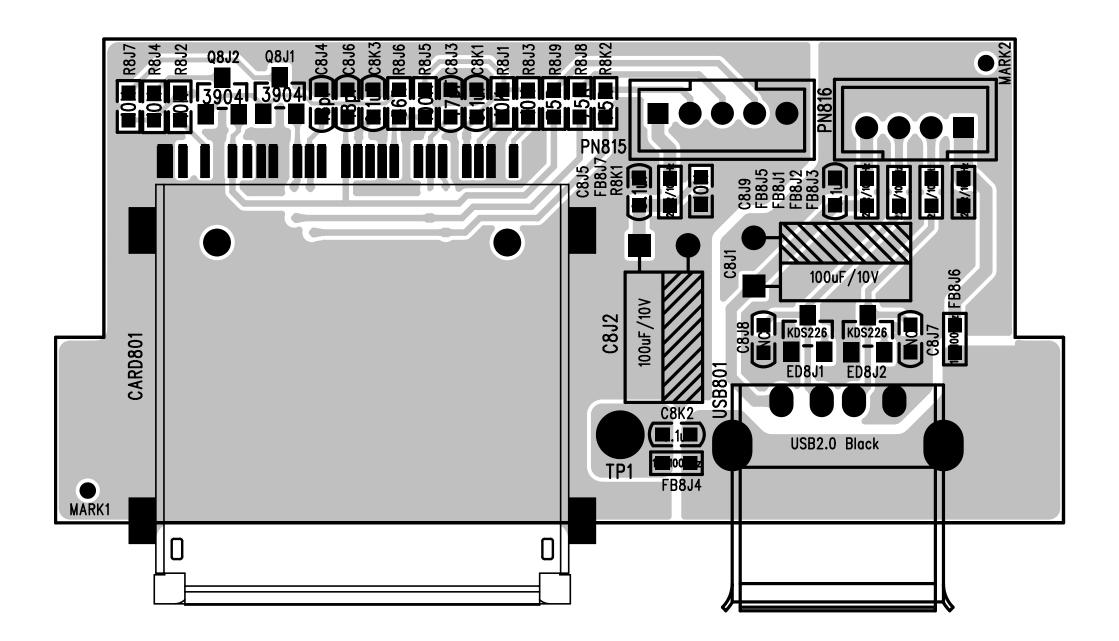

| 8. BLOCK DIAGRAM                                       | 135     |

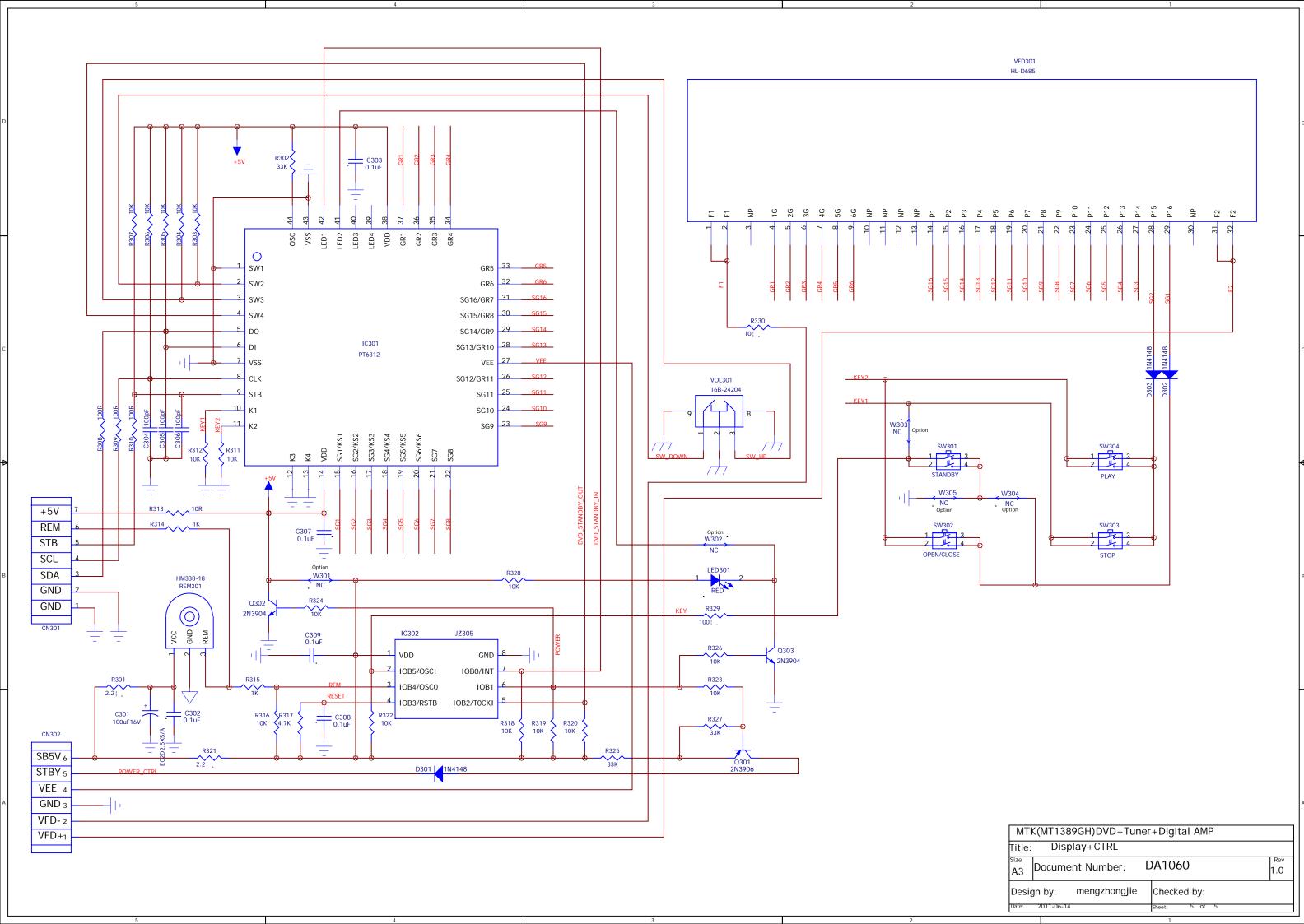

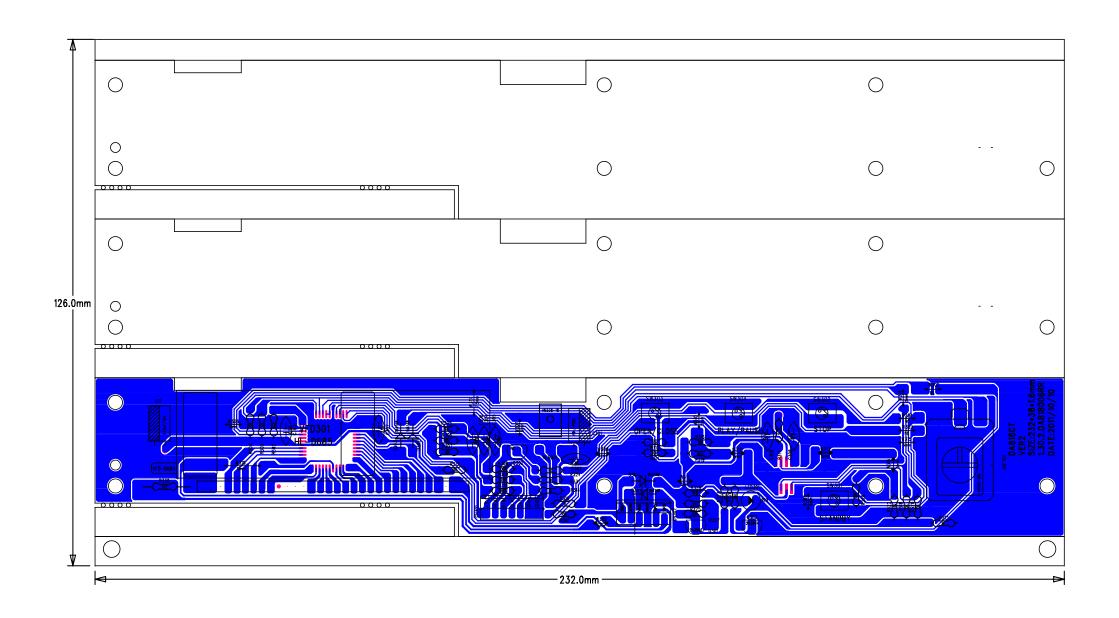

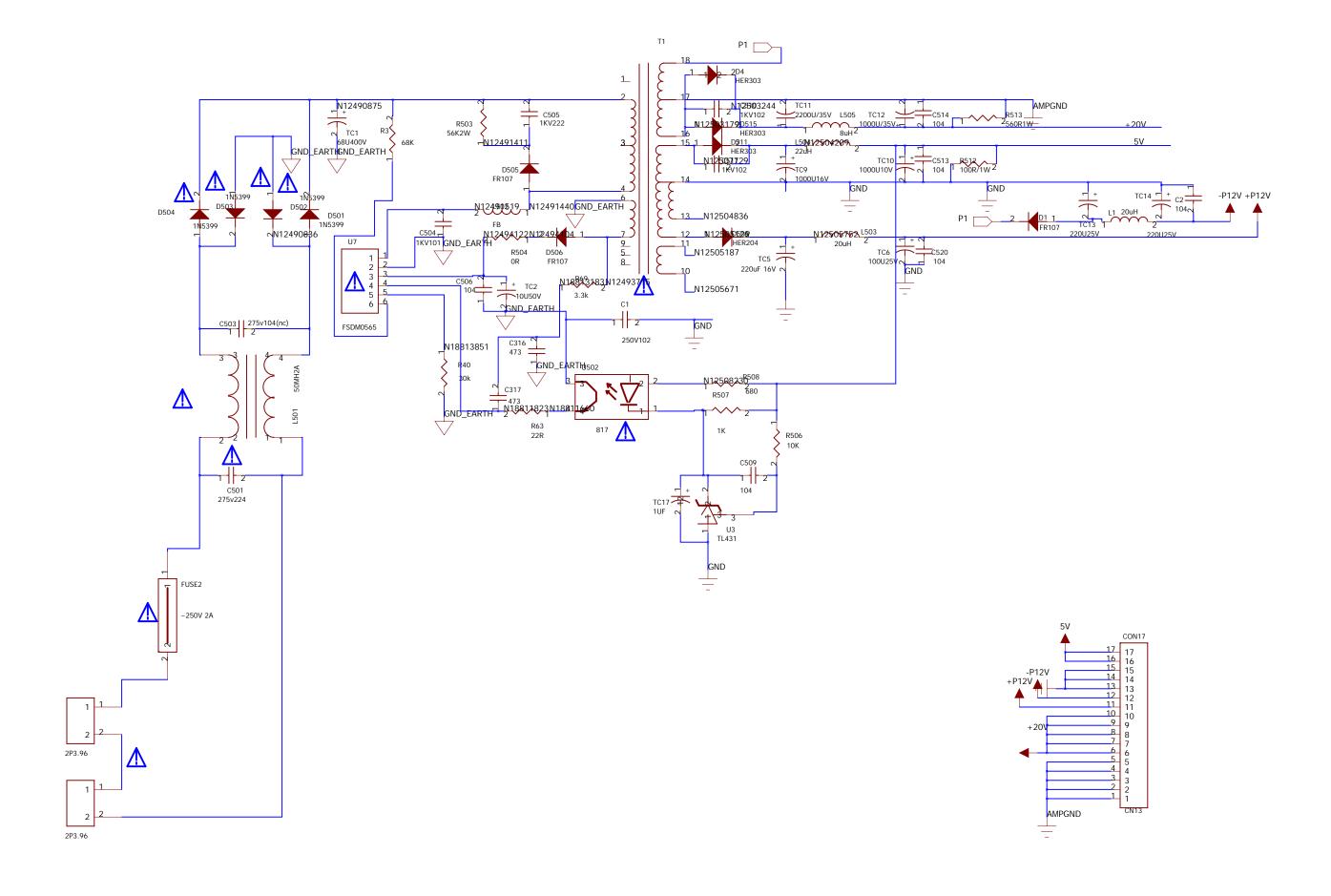

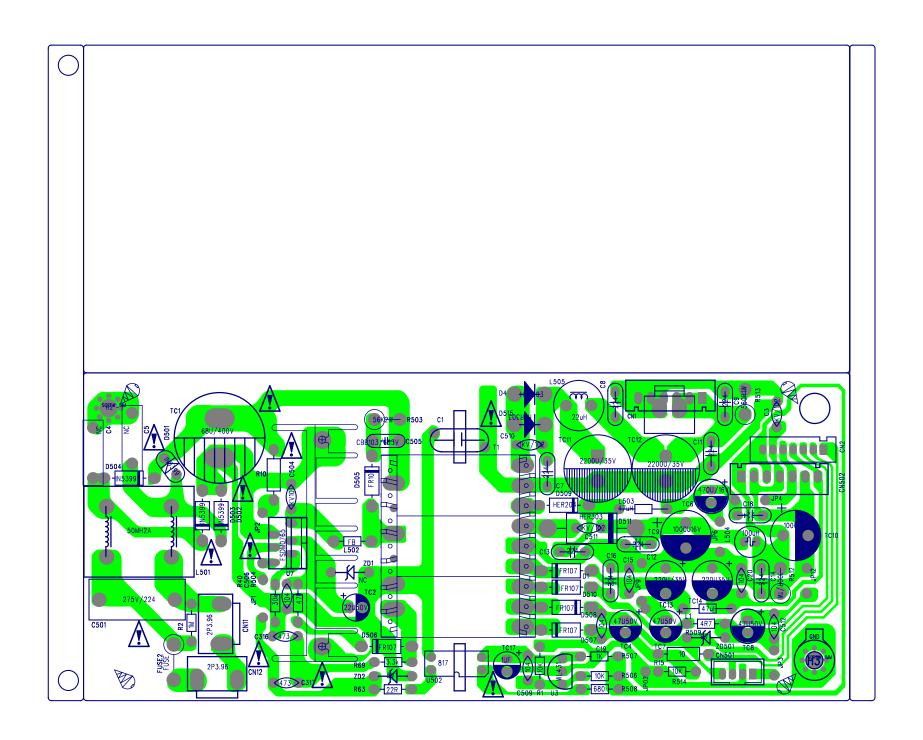

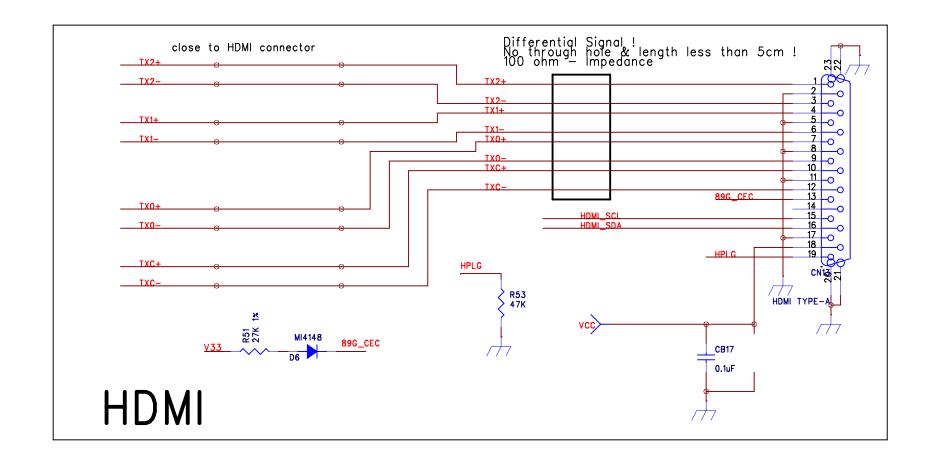

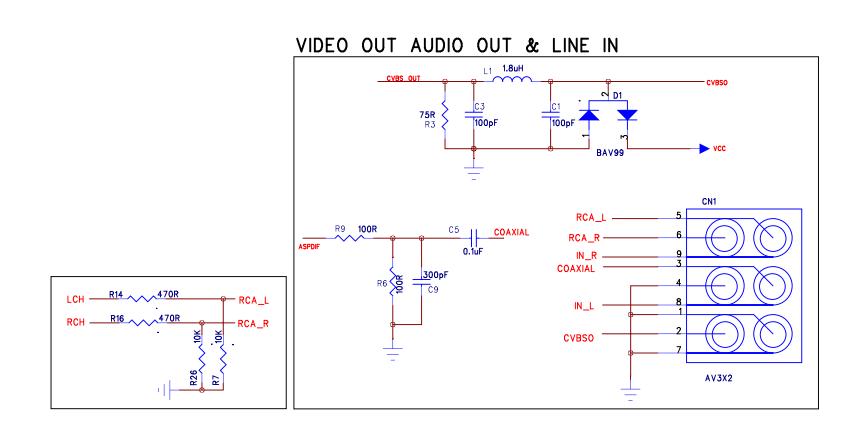

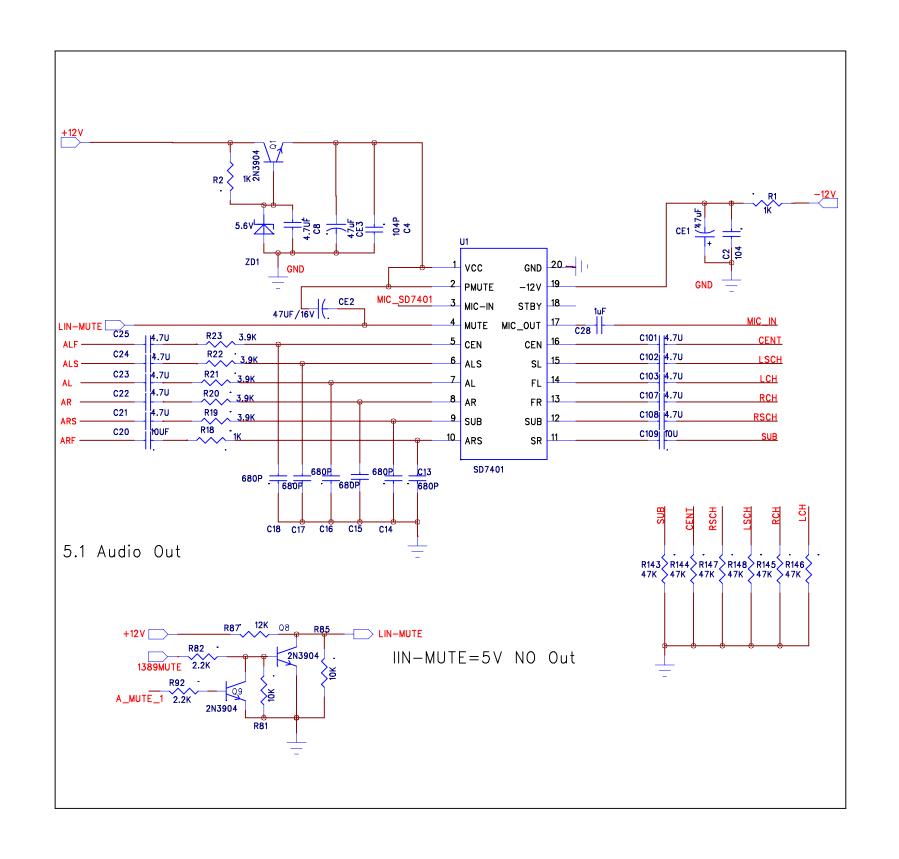

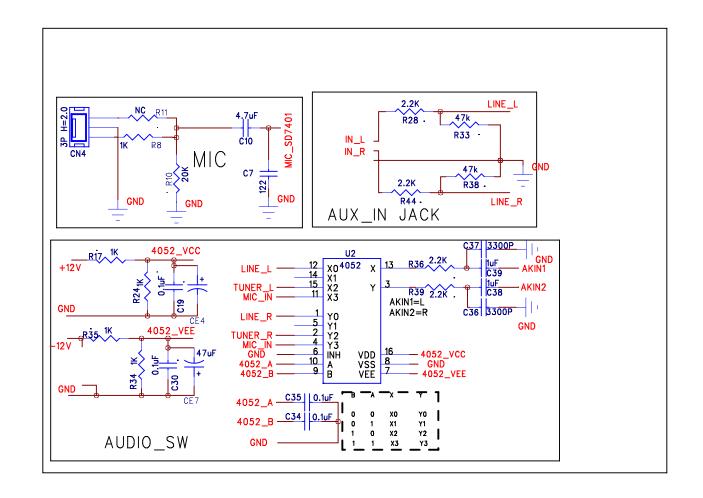

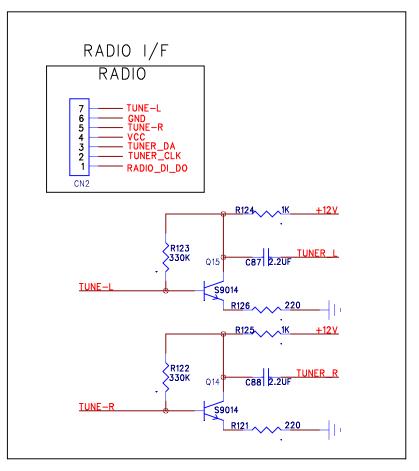

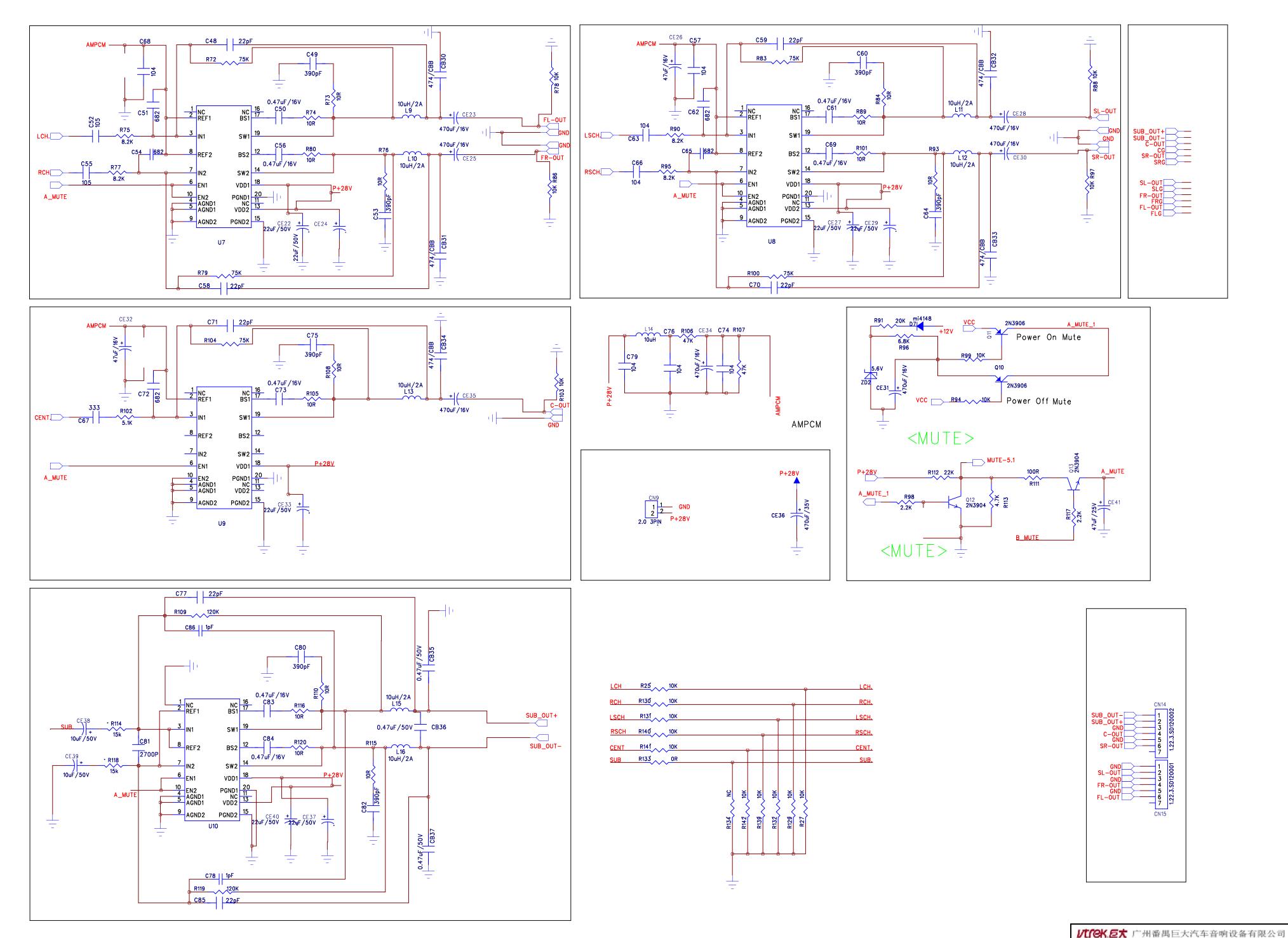

| 9. CIRCUIT DIAGRAMS AND WIRING DIAGRAM:                | 106 144 |

# 1. PRECAUTIONS

# 1-1 Safety Precautions

- 1) Before returning an instrument to the customer, always make a safety check of the entire instrument, including, but not limited to, the following items:

- (1) Be sure that no built-in protective devices are defective or have been defeated during servicing.

- (1) Protective shields are provided to protect both the technician and the customer. Correctly replace all missing protective shields, including any remove for servicing convenience.

- (2) When reinstalling the chassis and/or other assembly in the cabinet, be sure to put back in place all protective devices, including, but not limited to, nonmetallic control knobs, insulating fish papers, adjustment and compartment covers/shields, and isolation resistor/capacitor networks. Do not operate this instrument or permit it to be operated without all protective devices correctly installed and functioning.

- (2) Be sure that there are no cabinet opening through which adults or children might be able to insert their fingers and contact a hazardous voltage. Such openings include, but are not limited to, excessively wide cabinet ventilation slots, and an improperly fitted and/or incorrectly secured cabinet back cover.

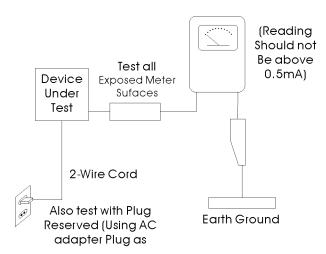

- (3) Leakage Current Hot Check-With the instrument completely reassembled, plug the AC line cord directly into a 120V AC outlet. (Do not use an isolation transformer during this test.) Use a leakage current tester or a metering system that complies with American National Standards institute (ANSI) C101.1 Leakage.

Current for **Appliances** and underwriters Laboratories (UL) 1270 (40.7).With instrument's AC switch first in the ON position and then in the OFF position, measure from a known earth ground (metal water pipe, conduit, etc.) to all exposed metal parts of the instrument (antennas, handle brackets, metal cabinets, screwheads, metallic overlays, control shafts, etc.), especially and exposed metal parts that offer an electrical return path to the chassis.

Any current measured must not exceed 0.5mA. Reverse the instrument power cord plug in the outlet and repeat the test.

AC Leakage Test

Any measurements not within the limits specified herein indicate a potential shock hazard that must be eliminated before returning the instrument to the customer.

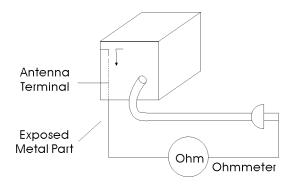

(4) Insulation Resistance Test Cold Check-(1) Unplug the power supply cord and connect a jumper wore between the two prongs of the plug. (2) Turn on the power switch of the instrument. (3) Measure the resistance with an ohmmeter between the jumpered AC plug and all exposed metallic cabinet parts on the instrument, such as screwheads, antenna, control shafts, handle brackets, etc. When an exposed metallic part has a return path to the chassis, the reading should be between 1 and 5.2 megohm. When there is no return path to the chassis, the reading must be infinite. If the reading is not within the limits specified, there is the possibility of a shock hazard, and the instrument must be re-pared and rechecked before it is returned to the customer.

Insulation Resistance Test

- 2) Read and comply with all caution and safety related notes non or inside the cabinet, or on the chassis.

- 3) Design Alteration Warning-Do not alter of add to the mechanical or electrical design of this instrument. Design alterations and additions, including but not limited to, circuit modifications and the addition of items such as auxiliary audio output connections, might alter the safety characteristics of this instrument and create a hazard to the user. Any design alterations or additions will make you, the service, responsible for personal injury or property damage resulting there from.

- 4) Observe original lead dress. Take extra care to assure correct lead dress in the following areas: (1) near sharp edges, (2) near thermally hot parts (be sure that leads and components do not touch thermally hot parts), (3) the AC supply, (4) high voltage, and (5) antenna wiring. Always inspect in all areas for pinched, out-of-place, or frayed wiring. Do not change spacing between a component and the printed-circuit board, Check the AC power cord for damage.

# 1-2 Servicing Precautions

**CAUTION:** Before servicing Instruments covered by this service manual and its supplements, read and follow the Safety Precautions section of this manual.

**Note:** If unforeseen circument create conflict between the following servicing precautions and any of the safety precautions, always follow the safety precautions. Remember; Safety First

#### 1-2-1 General Serving Precautions

- a. Always unplug the instrument's AC power cord from the AC power source before (1) removing or reinstalling any component, circuit board, module or any other instrument assembly. (2) disconnecting any instrument electrical plug or other electrical connection. (3) connecting a test substitute in parallel with an electrolytic capacitor in the instrument.

- b. Do not defeat any plug/socket B+ voltage interlocks with which instruments covered by this service manual might be equipped.

- c. Do not apply AC power to this instrument and/or any of its electrical assemblies unless all solid-state device heat sinks are correctly installed.

- d. Always connect a test instrument's ground lead to the instrument chassis ground before connecting the test instrument positive lead. Always remove the test instrument ground lead

- 5) Components, parts, and/or wiring that appear to have overheated or that are otherwise damaged should be replaced with components, parts and/or wiring that meet original specifications. Additionally determine the cause of overheating and/or damage and, if necessary, take corrective action to remove and potential safety hazard.

- 6) Product Safety Notice-Some electrical and mechanical parts have special safety-related characteristics which are often not evident from visual inspection, nor can the protection they give necessarily be obtained by replacing them with components rated for higher voltage, wattage, etc. Parts that have special safety characteristics are identified by shading, an ( ) or a ( ) on schematics and parts lists. Use of a substitute replacement that does not have the same safety characteristics as the recommended replacement part might created shock, fire and/or other hazards. Product safety is under review continuously and new instructions are issued whenever appropriate.

last.

**Note:** Refer to the Safety Precautions section ground lead last.

- (2) The service precautions are indicated or printed on the cabinet, chassis or components. When servicing, follow the printed or indicated service precautions and service materials.

- (3) The components used in the unit have a specified flame resistance and dielectric strength.

When replacing components, use components which have the same ratings, by ( ) or by ( ) in the circuit diagram are important for safety or for the characteristics of the unit. Always replace them with the exact replacement components.

- (4) An insulation tube or tape is sometimes used and some components are raised above the printed wiring board for safety. The internal wiring is sometimes clamped to prevent contact with heating components. Install such elements as they were.

- (5) After servicing, always check that the removed screws, components, and wiring have been installed correctly and that the portion around the serviced part has not been damaged and so on. Further, check the insulation between the blades of the attachment plus and accessible conductive parts.

#### 1-2-2 Insulation Checking Procedure

Disconnect the attachment plug from the AC outlet and turn the power ON. Connect the insulation resistance meter (500V) to the blades of the attachment plug. The insulation resistance between each blade of the

attachment plug and accessible conductive parts (see note) should be more than 1 Megohm.

**Note:** Accessible conductive parts include metal panels, input terminals, earphone jacks, etc.

#### 1-3 ESD Precautions

#### **Electrostatically Sensitive Devices (ESD)**

Some semiconductor (solid static electricity) devices can be damaged easily by static electricity.

Such compo9nents commonly are called Electrostatically Sensitive Devices (ESD). Examples of typical ESD devices are integrated circuits and some field-effect transistors and semiconductor chip components. The following techniques of component damage caused by static electricity.

- (1) immediately before handling any semiconductor components or semiconductor-equipped assembly, drain off any electrostatic charge on your body by touching a known earth ground. Alternatively, obtain and wear a commercially available discharging wrist strap device, which should be removed for potential shock reasons prior to applying power to the unit under test.

- (2) after removing an electrical assembly equipped with ESD devices, place the assembly on a conductive surface such as aluminum foil, to prevent electrostatic charge buildup or exposure of the assembly.

- (3) Use only a grounded-tip soldering iron to solder or unsolder ESD device.

- (4) Use only an anti-static solder removal devices.

Some solder removal devices not classified as "anti-static" can generate electrical charges sufficient to damage ESD devices.

- (5) Do not use freon-propelled chemicals. These can generate electrical charges sufficient to damage ESD devices.

- (6) Do not remove a replacement ESD device from its protective package until immediately before you are ready to install it. (Most replacement ES devices are packaged with leads electrically shorted together by conductive foam, aluminum foil or comparable conductive materials).

- (7) Immediately before removing the protective materials from the leads of a replacement ES device touch the protective material to the chassis or circuit assembly into which the device will be installed.

**CAUTION:** Be sure no power is applied to the chassis or circuit, and observe all other safety precautions.

(8) Minimize bodily motions when handling unpackaged replacement ESD devices. (Otherwise harmless motion such as the brushing together of your clothes fabric or the lifting of your foot from a carpeted floor can generate static electricity sufficient to damage an ESD device).

Version 1.0

Specifications are subject to change without notice

MT1389GH

High Definition DVD Player SOC with HDMI™ Tx Approval Sheet

# **Revision History**

| Revised date | Contents of revision    | Reason for revision | Page Remarks |

|--------------|-------------------------|---------------------|--------------|

| 2009 4 8     | 1 <sup>st</sup> Release | Initial Version     | Ver 1.0      |

|              |                         | Highor              |              |

|              | diatexconflic           | S.                  |              |

|              | digiek                  |                     |              |

| Me           |                         |                     |              |

|              |                         |                     |              |

# Contents of Specifications

| No | Specifications                 | Page |

|----|--------------------------------|------|

|    | Revision History               | 1    |

|    | Contents of Specification      | 2    |

|    |                                | 1    |

| 1  | <u>Applications</u>            | 3    |

| 2  | <u>Type</u>                    | 3    |

| 3  | <u>Usage</u>                   | 3    |

| 4  | <u>Structure</u>               | 3    |

| 5  | <u>Function</u>                | 4    |

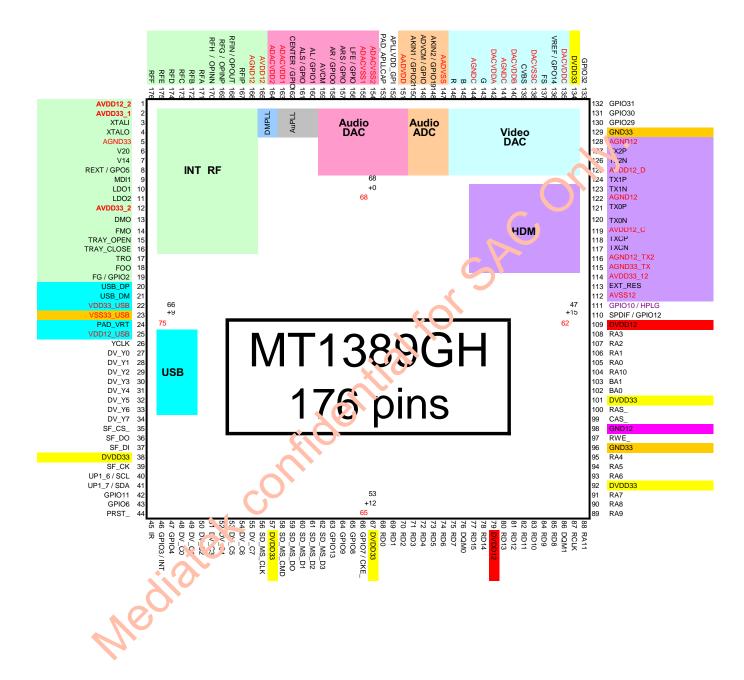

| 6  | <u>Pin Assignment</u>          | 23   |

| 7  | Absolute Maximum Ratings       | 24   |

| 8  | Recommend Operation Conditions | 24   |

| 9  | Electrical Characteristics     | 25   |

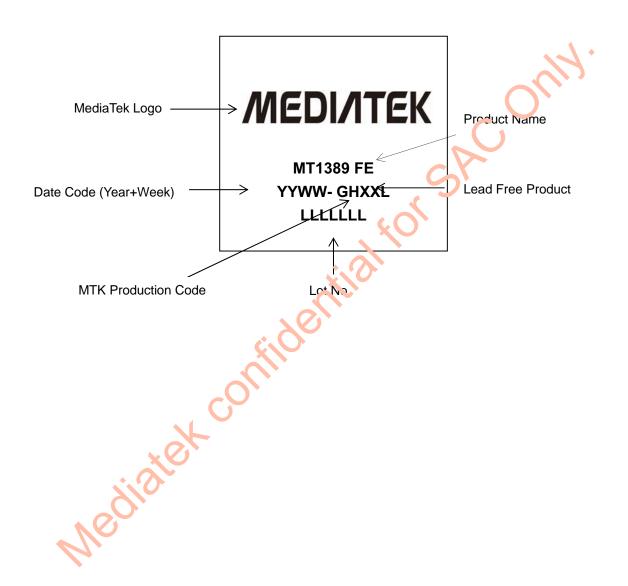

| 10 | Marking on Devices             | 35   |

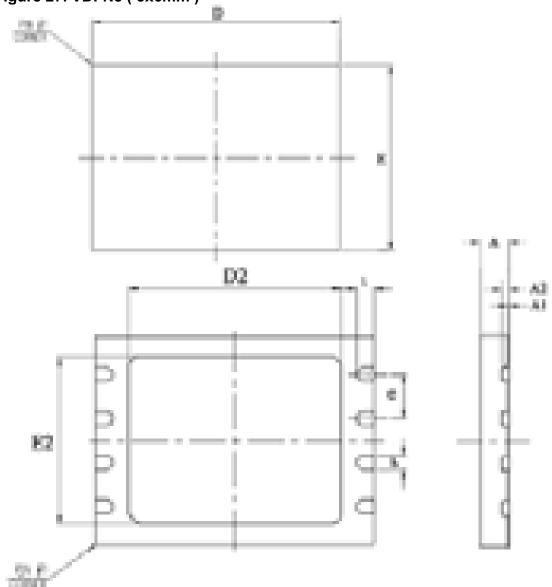

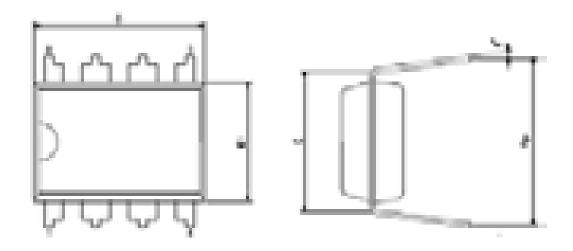

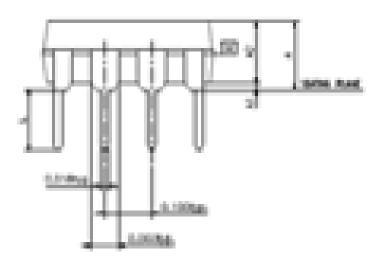

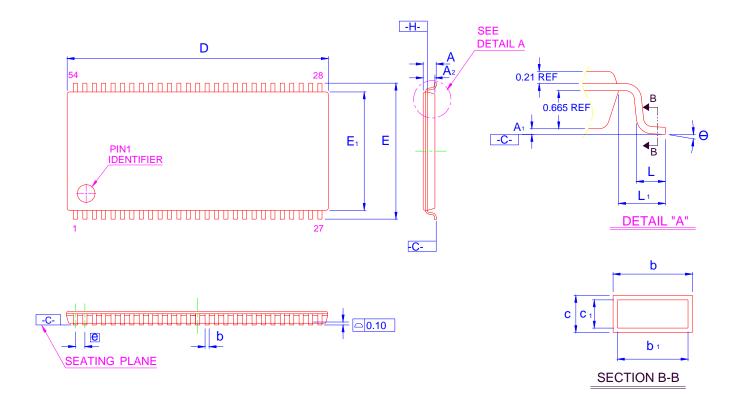

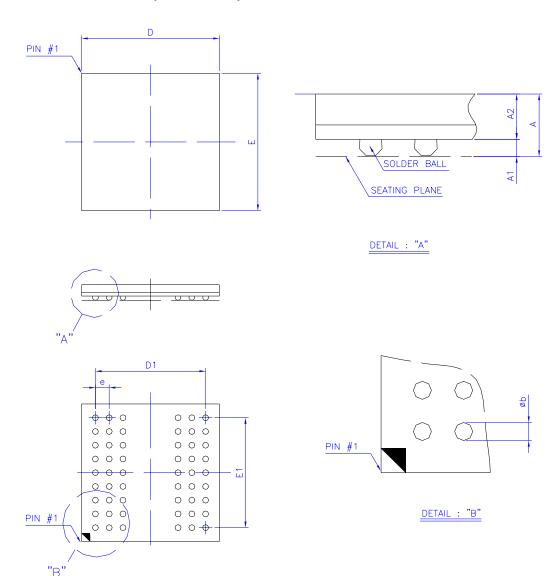

| 11 | Package Description            | 35   |

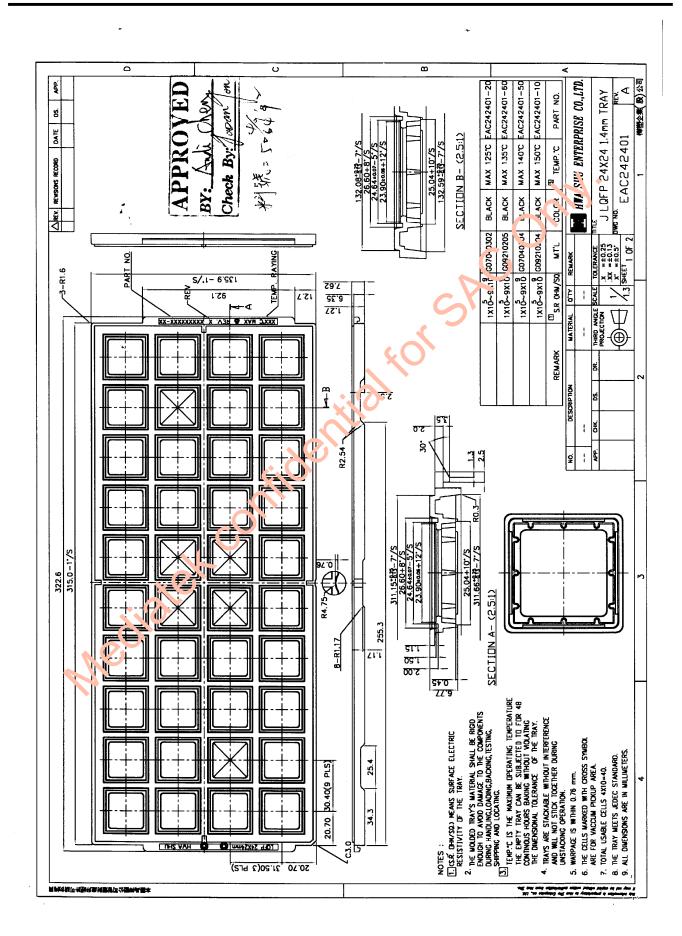

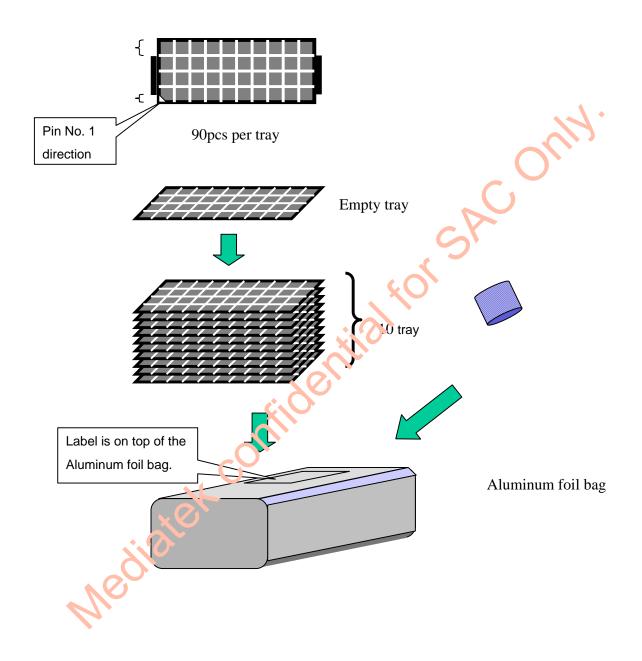

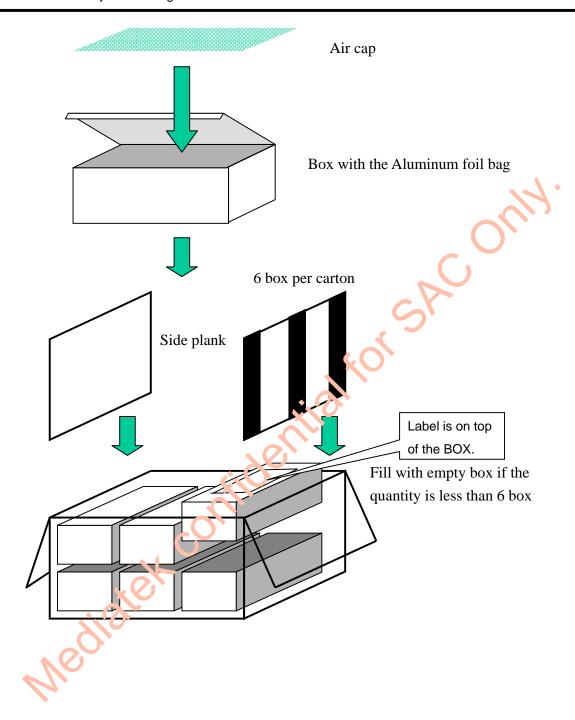

| 12 | Packing Description            | 37   |

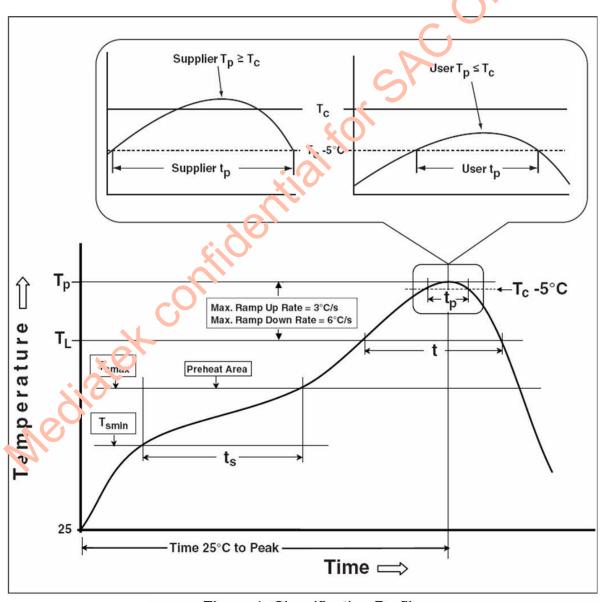

| 13 | Solder-Reflow Condition        | 42   |

| 14 | Manual Solder Condition        | 44   |

| 15 | Storage Condition              | 44   |

| 16 | <u>Other</u>                   | 44   |

|    | diatek                         |      |

# 1 Applications

This present specifications are applied to IC MT1389GH.

# 2 Type

MT1389GH

# 3 Usage

High Definition DVD Player SOC with HDMI<sup>™</sup> Tx

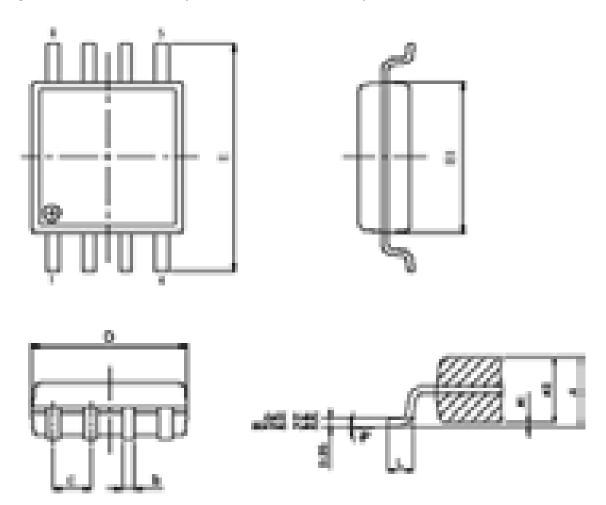

#### 4 Structure

0.13um CMOS process, Silicon material, Monolithic IC, 176 pin LQFP, 2.3/1.2 Dual operation voltages.

<sup>1</sup> "HDMI<sup>TM</sup>, the HDMI<sup>TM</sup> logo and High-Definition Multimedia Interface are trademarks or registered trademark of HDMI<sup>TM</sup> Licensing LLC."

#### 5 Function

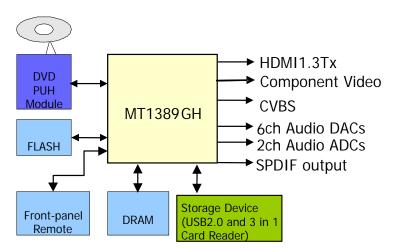

#### 5-1 General Description

MediaTek MT1389GH is a cost-effective DVD system-on-chip (SOC) which incorporates advanced features like MPEG-4 video decoder, high quality TV encoder ,state-of-art de-interlace processing, and HDMI™ 1.3 compatible transmitter. The MT1389GH enables consumer electronics manufacturers to build high quality, USB2.0, MS/SD/MMC reader, feature-rich DVD players or any other home entertainment audio/video devices.

**World-Leading Technology:** Based on MediaTek's world-leading DVD player SOC architecture, the MT1389GH is the New generation of the DVD player SOC. It integrates the MediaTek 3<sup>rd</sup> generation ront-end digital RF amplifier and the Servo/MPEG AV decoder.

Enjoy the attractive video on digital TV: The most popular HDTV input format is HDMI™ interface and it provides up to 1080P high resolution video output and high quality audio output

**Rich Feature for High Valued Product:** To enrich the feature of DVD player, the MT1389GH equips a simplified MPEG-4 advanced simple profile (ASP) video decoder to fully support the DivX<sup>2</sup> Home Theater profile. It makes the MT1389GH-based DVD player be capable of playback MF/EC-4 content which become more and more popular.

Incredible Audio/Video Quality: The progressive scan of the MT1389GH utilized MediaTek's MDDi™ advanced motion-adaptive de-interlace algorithm to achieve the best movie/video playback. It also supports a patent-pending edge-preserving algorithm to remover the saw-tooth effect. The 148MHz/12-bit video DACs provide users a whole new viewing experience. It also supports a 3:2 pull down algorithm to give the best film effect. Built-in 6ch audio DACs and 2ch audio ADCs could give the variable function solutions.

High Performance Memory Storage Device: As the core of DVD players need more capability to support current multimedia contents. The MT1239GH provides the interface for the 3-in-1 card reader, which supports Memory-Stick, Secure Digital Memory Card, and MultiMediaCard, to connect with the mainstream digital camera FLASH cards. For the USB application, we adopt USB2.0 High speed specification to reach rich-contents transference. USB 2.0 High speed will support for high-speed devices. USB 2.0 High Speed is suitable for high-performance a vives such as high-density storage devices. In addition, USB 2.0 High Speed supports USB 1.0/1.1 devices affering impressive and even better compatibility to customers

\_

<sup>&</sup>lt;sup>2</sup> DivX is a trademark of DivXNetworks

<sup>&</sup>lt;sup>3</sup> USB High Speed: maximum 480Mbit/sec. USB Full Speed: maximum 12Mbit/sec.

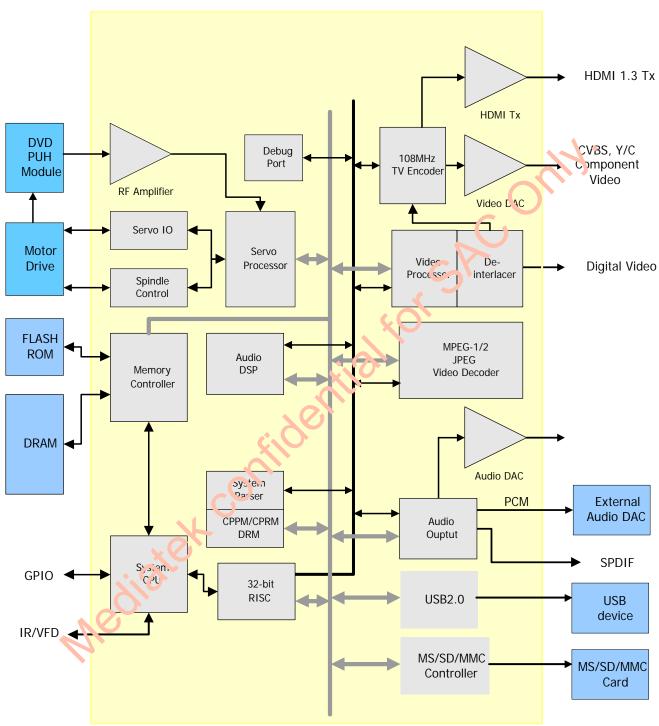

**DVD Player System Diagram**

# **Key Features**

RF/Servo/MPEG Integration

DivX Home Theater Level MPEG4 ASP Video decoder

Support DivX Ultra

High Performance Audio Processor

Progressive Scan

Internal 6CH Audio DAC

Internal 2CH Audio ADC

MDDi: Motion-Adaptive Pure Edge™ De-interlacing

148MHz/12-bit TV Encouer

USB2.0 High Speed (Host)

3-in-1 MS/SD/MMC reader

HDMI M1.3 Tx with CEC support

USB2.0 High Speed (Host)

# Applications

Sundard DVD Players

#### 5-2 Key Features

- RF/Servo/MPEG Integration

- Embedded 6ch Audio DAC

- Embedded 2ch Audio ADC for Karacka

- High Performance Audio Processor

- High Performance Progressive Video Processor

- HDMI<sup>™</sup>1.3 Tx with CFC support

- MDDi: Motion-Adaptive, Pure Edge<sup>TM</sup> De-interlacing

- High Quality 1 8MHz/12-bit TV Encoder

- Scapert DivX Ultra

- USB 2.0 High-Speed

#### 5-3 General Feature lists

#### Super Integration DVD player single chip

- High performance analog RF amplifier

- Servo controller and data channel processing

- MPEG-1/MPEG-2/JPEG video

- Dolby AC-3/DTS Decoder

- Unified memory architecture

- Versatile video scaling & quality enhancement

- OSD & Sub-picture

- Built-in clock generator

- Built-in progressive video processor

- HDMI<sup>™</sup>1.3 Tx with CEC support

- MDDi: Motion-Adaptive, Pure Edge<sup>™</sup> De-interlacing

- Built-in High Quality 148MHz/12-bit TV Encoder

- Audio effect post-processor

- Built-in 5.1-ch Audio DAC

- Built-in 2-ch Audio ADC for Karaoke

- USB 2.0 High-Speed

- MS/SD/MMC 3-in-1 card reader

- Build-in DIR for Home Theater

#### ■ Speed Performance on Servo/Channel Decoding

- DVD-ROM up to 4XS

- CD-ROM up to 24XS

#### ■ Channel Data Processor

- Digital data slicer for small jitter capability

- Built-in high performance data PLL for channel data demodulation

- EFM/EFM+ data demodulation

- Enhanced channel data frame sync protection & DVD-ROM sector sync protection

#### ■ Servo Control and Spindle Mour Control

- Programmable frequency error gain and phase error gain of spindle PLL to control spindle motor on CLV and CAV mode

- Built-in ADCs and DACs for digital servo control

- Provide 2 Jeneral PWM

- Tray control can be PWM output or digital output

#### ■ Embedded Micro controller

- Built-in 8032 micro controller

- Built-in internal 373 and 8-bit programmable lower address port

- 1024-bytes on-chip RAM

- Up to 2M bytes FLASH-programming interface

- Supports 5/3.3-Volt. FLASH interface

- Supports power-down mode

- Supports additional serial port

#### ■ DVD-ROM/CD-ROM Decoding Logic

- High-speed ECC logic capable of correcting one error per each P-codeword or Q-codeword

- Automatic sector Mode and Form detection

- Automatic sector Header verification

- Decoder Error Notification Interrupt that signals various decoder errors

- Provide error correction acceleration

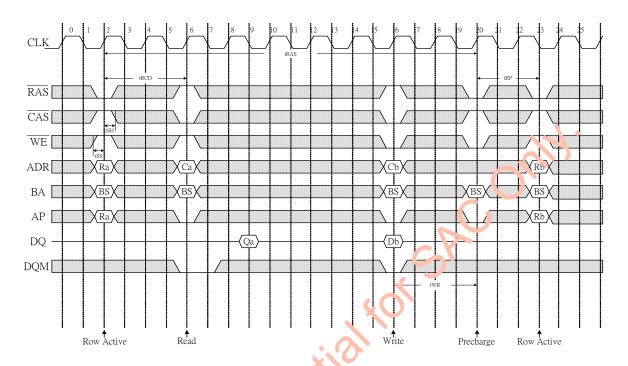

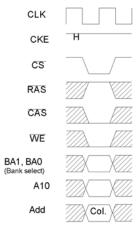

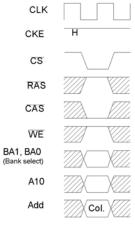

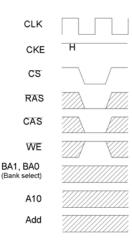

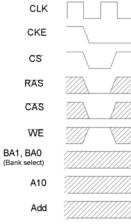

#### **■** Buffer Memory Controller

- Supports 16Mb/32Mb/6 4Mb/1 28Mb SDRAM

- Supports 16-bit SDPAM data bus

- Provides the self-efresh mode SDRAM

- Block-based sector addressing

#### ■ Video Decous

- Deccres MPEG1 video and MPEG2 main level, main profile video (720/480 and 720x576)

- Necodes MPEG-4 Advanced Simple Profile

- Support DivX 3.11/4.x/5.x Home Theater Profile

- Support DivX Ultra

- Smooth digest view function with I, P and B picture decoding

- Baseline, extended-sequential and progressive JPEG image decoding

- Support CD-G titles

#### Video/OSD/SPU/HLI Processor

- Arbitrary ratio vertical/horizontal scaling of video, from 0.25X to 256X

- 65535/256/16/4/2-color bitmap format OSD,

- 256/16 color RLC format OSD

- Automatic scrolling of OSD image

- Support 480i/480p/576i/576p Display

- Support 720p/1080i Display

- Support 1080p Display

- Simultaneous HD/SD output

#### ■ 2-D Graphic Engine

- Support decode Text and Bitmap

- Support line, rectangle, and gradient fill

- Support bitblt

- Chroma key copy operation

#### ■ Audio Effect Processing

- Dolby Digital (AC-3) decoding

- DTS decoding

- MPEG-1 layer 1/layer 2 audio decoding

- High Definition Compatible Digital (HDCD)

- Windows Media Audio (WMA)

- Dolby ProLogic II

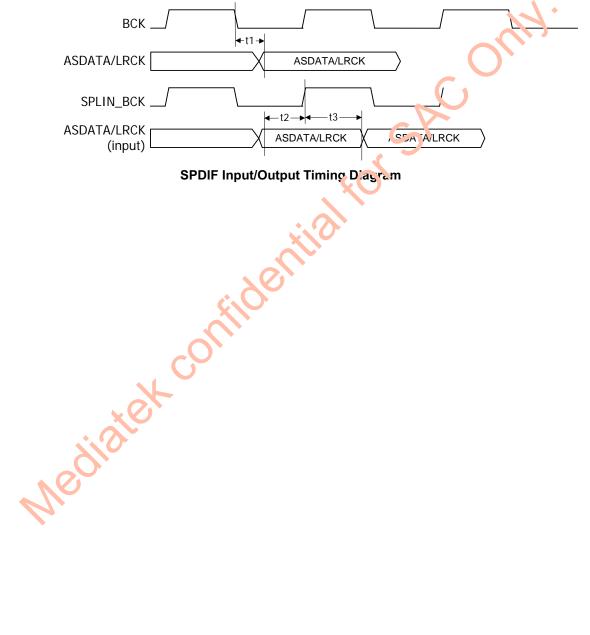

- IEC 60958/61937 output

- PCM / bit stream / mute mode

- Pink noise and white noise generator

- Karaoke functions

- Microphone echo

- Microphone tone control

- Vocal mute/vocal assistant

- Kev shift up to +/- 8 kevs

- Chorus/Flanger/Harmony/Reverb

- Channel equalizer

- 3D surround processing include virtual surround and speaker separation

#### TV Encoder

- Four 148MHz/12-bit DACs

- Support NTSC, PAL-BDGHINM, PAL-60

- Support 525p, 625p progressive TV format

- Support Macrovision 7.1 L1 and 1.3 (525p/625p).

- CGMS-AWSS

- Closed Caption

#### ■ MDDi <sup>™</sup> Progressive Scan Video

- Automatic detect film or video source

- 3:2 pull down source detection

- Advanced Motion adaptive de-interlace

- PureEdge<sup>™</sup> edge preserving technology

- PureEdge<sup>™</sup> edge preserving technology V2

- Minimum external memory requirement

#### ■ HDMI<sup>™</sup> Tx V1.3

- Compatible with ND 1 1.3, DVI 1.0, HDCP 1.3

- Support EIA/CEA 831B 480i/ 480p/ 576i/ 576p/ 720p/ 1080i/ 1080p

- Maximum Channels 192k audio output

- Support audio sampling rate conversion

- Hot-ping and power-on detection

- HDMI™ display full screen

- CEC function support

- Deep Color support

#### Image Resizer

#### Video case

- Support progressive / Interlaced frame scaling

- Support input & output maximum size: 4096x4096

JPEG case

- Input memory layout of source images must be scan line based

- Deal with one block line (height:8 / 16) each round

- Input maximum size: 65535x65535

- Output maximum size: 4096x4096

- Support a output scaling window of arbitrary location in an output frame buffer

- Y/Cb/Cr separated

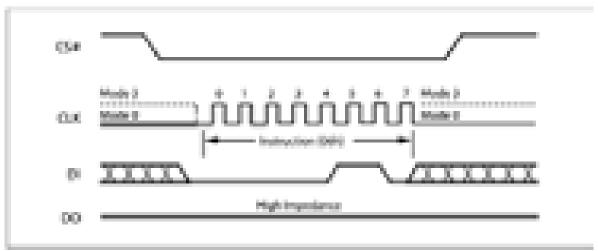

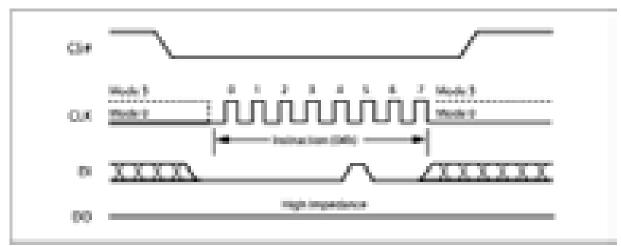

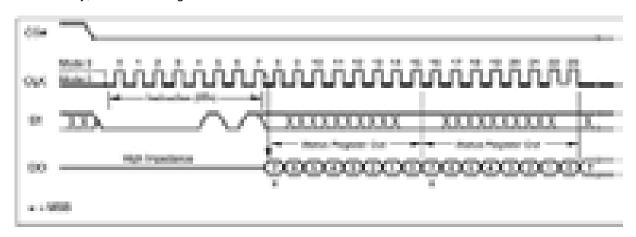

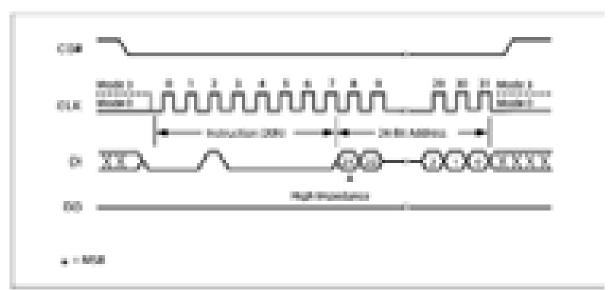

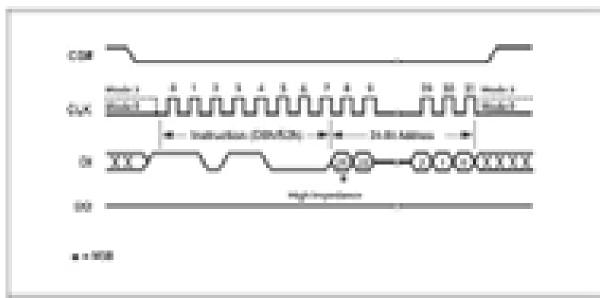

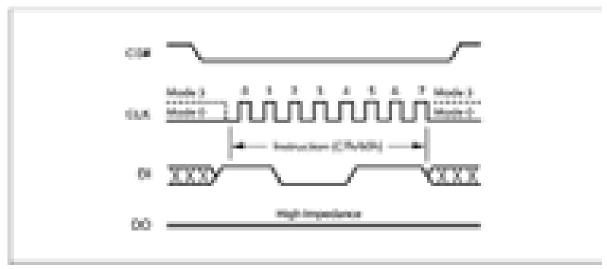

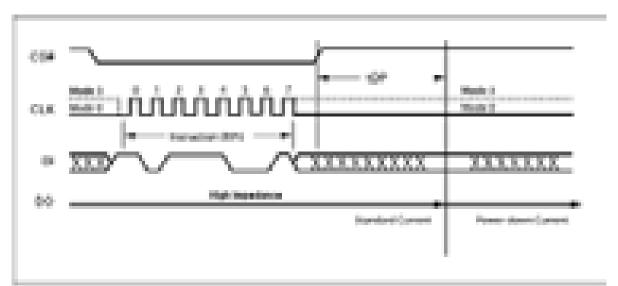

#### Serial Flash Interface

Supports 41/lb/cMb/16Mb/32Mb/64Mb SPI interface Serial Flasin

#### ■ External merface

- USB2.0 High Speed (Host)

- Memory-Stick, Secure Digital Memory Card, and MultiMediaCard Interface

#### Outline

- 176-pins LQFP package

- 3.3/1.2-Volt. Dual operating voltages

# Version 1.0

High Definition DVD Player

SOC with HDMI™ Tx

Approval Sheet

MT1389GH

Specifications are subject to change without notice

#### **General Feature - Third Party Proprietary Right**

#### 1. Dolby License

Supply of this Implementation of Dolby technology does not convey a license nor imply a right under any patent, or any other industrial or intellectual property right of Dolby Laboratories, to use this Implementation in any finished end-user or ready-to-use final product. It is hereby notified that a license for such use is required from Dolby Laboratories.

2. Macrovision License

This device is protected by U.S. patent numbers 4,631,603, 4,577,216, 4,819,098 and other intellectual property rights.

3. DTS License

©1996-2006 DTS, Inc.

4. Microsoft License

This product included technology owned by Microsoft Corporation and canno's be used or distributed without a license from Microsoft GP.

#### 5-4 Pin Definitions

#### Abbreviations:

SR: Slew RatePU: Pull UpPD: Pull Down

• SMT: Schmitt Trigger

• 4mA~16mA: Output buffer driving strength.

| Pin | Main     | Alt.           | Туре                                         | Description                                                                                                                                   |

|-----|----------|----------------|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

|     |          |                | Analog In                                    | iterface (85)                                                                                                                                 |

| 167 | RFIP     |                | Analog Input                                 | AC coupled DVD RF signal input RFIP                                                                                                           |

| 168 | RFIN     | OPOUT<br>GPI36 | Analog Input<br>Non-pull                     | AC coupled DVD R - cignal input RFIN     GPI36                                                                                                |

| 169 | RFG      | OPINP          | Analog Input                                 | Main beam, RF AC input path                                                                                                                   |

| 170 | RFH      | OPINN          | Analog Input                                 | Main bea.n, RF AC input path                                                                                                                  |

| 171 | RFA      |                | Analog Input                                 | RF mail beam input A                                                                                                                          |

| 172 | RFB      |                | Analog Input                                 | RF main beam input B                                                                                                                          |

| 173 | RFC      |                | Analog Input                                 | KF main beam input C                                                                                                                          |

| 174 | RFD      |                | Analog Input                                 | RF main beam input D                                                                                                                          |

| 175 | RFE      |                | Analog Input                                 | RF sub beam input E                                                                                                                           |

| 176 | RFF      |                | Analog Input                                 | RF sub beam input E                                                                                                                           |

| 1   | AVDD12_2 |                | Analog Power                                 | Analog 1.2V power                                                                                                                             |

| 2   | AVDD33_1 |                | Analog Power                                 | Analog 3.3V power                                                                                                                             |

| 3   | XTALI    | X              | Input                                        | 27MHz crystal input                                                                                                                           |

| 4   | XTALO    |                | Output                                       | 27MHz crystal output                                                                                                                          |

| 5   | 4C(N))33 |                | Analog Ground                                | Analog 3.3V Ground                                                                                                                            |

| 6   | V20      |                | Analog output                                | Reference voltage 2.0V                                                                                                                        |

| 7   | V14      |                | Analog output                                | Reference voltage 1.4V                                                                                                                        |

| 8   | REXT     | GPO5           | Analog Input /<br>Digital output<br>Non-pull | Current reference input. It generates     reference current for RF path. Connect an     external 15K resistor to this pin and AVSS.      GPO5 |

| 9   | MDI1     |                | Analog Input                                 | Laser power monitor input                                                                                                                     |

| Pin | Main        | Alt.   | Туре                      | Description                                                      |

|-----|-------------|--------|---------------------------|------------------------------------------------------------------|

| 10  | LDO1        |        | Analog Output             | Laser driver output                                              |

| 11  | LDO2        |        | Analog Output             | Laser driver output                                              |

| 12  | AVDD33_2    |        | Analog Power              | Analog 3.3V power                                                |

| 13  | DMO         |        | Analog Output             | Disk motor control output. PWM output                            |

| 14  | FMO         |        | Analog Output             | Feed motor control. PWM output                                   |

| 15  | TRAY_OPEN   | GPI0   | Analog Output<br>Non-pull | Tray PWM output/Tray open output                                 |

| 16  | TRAY_CLOSE  | GPI0   | Analog Output<br>Non-pull | Tray PWM output/Tray close cutput                                |

| 17  | TRO         |        | Analog Output             | Tracking servo output. Furl output of tracking servo compensator |

| 18  | FOO         |        | Analog Output             | Focus servo out out. PDM output of focus servo compensato:       |

| 19  | FG          | GPIO2  | Analog Non-pull           | 1) Motor Hall sensor input 2) GPIC2                              |

| 20  | USB_DP      |        | Analog Inout              | U.B , ort DPLUS analog pin                                       |

| 21  | USB_DM      |        | Analog Inout              | USB port DMINUS analog pin                                       |

| 22  | VDD33_USB   |        | USB Porver                | USB Power pin 3.3V                                               |

| 23  | VSS33_USB   |        | USP G. ound               | USB Ground pin 3.3V                                              |

| 24  | PAD_VRT     | GPI037 | Araiog Inout              | USB generating reference current     GPIO37                      |

| 25  | VDD12_USB   |        | USB Power                 | USB Power pin 1.2V                                               |

| 112 | AVSS12      | .0     | Analog Ground             | Analog 1.2V Ground                                               |

| 113 | EXT_RES     |        | Analog Input              | EXTERNAL RESISTER FOR HDMI™ TX                                   |

| 114 | AVDD33_√PL⊾ |        | Analog Power              | 3.3V VDD FOR HDMI™ TX                                            |

| 115 | AG ND33_TX  |        | Analog Ground             | Analog 3.3V Ground                                               |

| 116 | .^GND12_TX2 |        | Analog Ground             | Analog 1.2V Ground                                               |

| 117 | TXCN        |        | Analog Output             | Negative TX CLK                                                  |

| 118 | TXCP        |        | Analog Output             | Postive TX CLK                                                   |

| 119 | AVDD12_TX1  |        | Analog Power              | 1.2V VDD FOR HDMI™ TX                                            |

| 120 | TX0N        |        | Analog Output             | Negative TX CH0                                                  |

| 121 | TX0P        |        | Analog Output             | Postive TX CH0                                                   |

| 122 | AGND12_TX1  |        | Analog Power              | 1.2V GND FOR HDMI™ TX                                            |

| 123 | TX1N        |        | Analog Output             | Negative TX CH1                                                  |

| Pin         | Main       | Alt.   | Туре                             | Description                                                                                       |

|-------------|------------|--------|----------------------------------|---------------------------------------------------------------------------------------------------|

| 124         | TX1P       |        | Analog Output                    | Postive TX CH1                                                                                    |

| 125         | AVDD12_TX0 |        | Analog Power                     | 1.2V VDD FOR HDMI™ TX                                                                             |

| 126         | TX2N       |        | Analog Output                    | Negative TX CH2                                                                                   |

| 127         | TX2P       |        | Analog Output                    | Postive TX CH2                                                                                    |

| 128         | AGND12_TXD |        | Analog Ground                    | Analog 1.2V Ground                                                                                |

| <b>13</b> 5 | DACVDDC    |        | Power                            | 3.3V power pin for video DAC circuitry                                                            |

| <b>13</b> 6 | VREF       | GPO14  | Analog / Digital Output/Non-pull | <ol> <li>Bandgap reference voltage</li> <li>GPO14</li> <li>AUDIO Mutc.</li> </ol>                 |

| 137         | FS         |        | Analog                           | Full scale adjustment (s ignest to use 560 ohm)                                                   |

| <b>13</b> 8 | DACVSSC    |        | Analog Ground                    | Analog 3.3V Grourd                                                                                |

| <b>13</b> 9 | CVBS       |        | Analog                           | Analog CVBS c C                                                                                   |

| 140         | DACVDDB    |        | Power                            | 3.3V power pin for video DAC circuitry                                                            |

| 141         | AGNDC      |        | Analog Ground                    | Analog 3V Ground                                                                                  |

| <b>14</b> 2 | DACVDDA    |        | Power                            | 3.4 power pin for video DAC circuitry                                                             |

| <b>14</b> 3 | Y/G        |        | Analog                           | Green, Y, SY, or CVBS                                                                             |

| <b>14</b> 4 | AGNDC      |        | Analog Ground                    | Analog 3.3V Ground                                                                                |

| <b>14</b> 5 | B/CB/PB    |        | Anaing                           | Blue, CB/PB, or SC                                                                                |

| <b>14</b> 6 | R/CR/PR    |        | Analog                           | Red, CR/PR, CVBS, or SY                                                                           |

| 147         | AADVSS     |        | Inalog Ground                    | Analog 3.3V Ground                                                                                |

| 148         | AKIN2      | GPIO19 | Analog Non-pull                  | 1) Audio ADC input 2 2) MCDATA 3) Audio Mute 4) HSYN/VSYN output 5) SPDIF output2 6) GPIO19 7) Y5 |

| 149         | ADVCM      | GPIO20 | Analog Non-pull                  | <ol> <li>Hotplug</li> <li>GPIO20</li> <li>Y6</li> </ol>                                           |

| Pin         | Main     | Alt.         | Туре                      | Description                                                                                                              |

|-------------|----------|--------------|---------------------------|--------------------------------------------------------------------------------------------------------------------------|

| 150         | AKIN1    | GPIO21       | Analog Non-pull           | <ol> <li>Audio ADC input 1</li> <li>Audio Mute</li> <li>HSYN/VSYN output</li> <li>GPIO21</li> <li>Y7</li> </ol>          |

|             |          |              |                           | 6) ASDATA3                                                                                                               |

| 151         | AADVDD   |              | Power                     | 3.3V power pin for 2ch audio ADC circuitry                                                                               |

| <b>15</b> 2 | APLLVDD3 | GPI034       | Power,PU                  | 1) 3.3V Power pin for audio cloc' circ iii.y 2) GPIO34                                                                   |

| <b>15</b> 3 | APLLCAP  | GPI035       | Analog InOut,<br>Non-pull | APLL external capacital reconnection     GPIO35                                                                          |

| 154         | ADACVSS2 |              | Analog Ground             | Analog 3.3V Ground                                                                                                       |

| 155         | ADACVSS1 |              | Analog Ground             | Analog 3 3V Gr. und                                                                                                      |

| 156         | LFE      | GPIO_LEF     | Analog Output<br>Non-pull | 1) Audio LAC sub-woofer channel output 2) While internal audio DAC not used: a. ACLK b. HSYN/VSYN output c. GPIO_LEF     |

| 157         | ARS      | GPIO_AR<br>S | Analog Ontput Non pu!!    | 1) Audio DAC right Surround channel output 2) While internal audio DAC not used: a. ABCK b. HSYN/VSYN output c. GPIO_ARS |

| 158         | AR       | GPIO_AR      | Analog Output<br>Non-pull | 1) Audio DAC right channel output 2) While internal audio DAC not used: a. ASDATA2 b. RXD2 c. GPIO_AR                    |

| 159         | AVCM     |              | Analog                    | Audio DAC reference voltage                                                                                              |

| 160         | N Cal    | GPIO_AL      | Analog Output<br>Non-pull | Audio DAC left channel output     While internal audio DAC not used:     a. ASDATA1     b. TXD2     c. GPIO_AL           |

| 161         | ALS      | GPIO         | Analog Output<br>Non-pull | Audio DAC left Surround channel output     While internal audio DAC not used:     a. ALRCK     b. GPIO                   |

| 162         | CENTER   | GPIO         | Analog Output<br>Non-pull | 1) Audio DAC center channel output 2) While internal audio DAC not used: a. ASDATA0 b. Audio Mute c. GPIO                |

| 163         | ADACVDD1 |              | Analog Power              | 3.3V power pin for audio DAC circuitry                                                                                   |

| Pin                                             | Main               | Alt.     | Туре                        | Description                                                                                                                                                                                     |  |  |  |  |  |

|-------------------------------------------------|--------------------|----------|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 164                                             | ADACVDD2           |          | Analog Power                | 3.3V power pin for audio DAC circuitry                                                                                                                                                          |  |  |  |  |  |

| 165                                             | AVDD12_1           |          | Analog Power                | Analog 1.2V power                                                                                                                                                                               |  |  |  |  |  |

| <b>16</b> 6                                     | AGND12             |          | Analog Ground               | Analog 1.2V Ground                                                                                                                                                                              |  |  |  |  |  |

|                                                 | General Power (7)  |          |                             |                                                                                                                                                                                                 |  |  |  |  |  |

| 79, 109                                         | DVDD12             |          | Power                       | 1.2V power pin for internal digital circuitry                                                                                                                                                   |  |  |  |  |  |

| 38, 57, 67,<br>92, 101                          | DVDD33             |          | Power                       | 3.3V power pin for internal digital circuity                                                                                                                                                    |  |  |  |  |  |

|                                                 | General Ground (2) |          |                             |                                                                                                                                                                                                 |  |  |  |  |  |

| 98                                              | DVSS12             |          | Ground                      | 1.2V ground pin for internal digital circuitry                                                                                                                                                  |  |  |  |  |  |

| 96                                              | DVSS33             |          | Ground                      | 3.3V ground pin for internal digital circuitry                                                                                                                                                  |  |  |  |  |  |

| Micro Controller , Flash Interface and GPIO(11) |                    |          |                             |                                                                                                                                                                                                 |  |  |  |  |  |

| 46                                              | GPIO3              | INT#     | InOut<br>8mA, SR<br>SMT     | 1) Ce eral purpose IO 3 2) Microcontroller port 3-1 2) Microcontroller external interrupt 1 4) MS_CLK SET B 5) IPOD_TXD 6) CEC                                                                  |  |  |  |  |  |

| 47                                              | GPIO4              | <b>V</b> | \nOut<br>4mA, PD            | <ol> <li>General purpose IO 4</li> <li>SD_CLK set B</li> <li>Microcontroller port 3-4 (Internal Pull-Up)</li> <li>MS_BS SET B</li> <li>ASDATA0</li> <li>ALRCK</li> </ol>                        |  |  |  |  |  |

| 43                                              | GPIO:              | S. S.    | InOut<br>4mA, PU            | <ol> <li>General purpose IO 6</li> <li>Microcontroller port 3-5 (Internal Pull-Up)</li> <li>Y3</li> <li>HSYN/VSYN output</li> <li>SD_CLK SET B</li> <li>MS_D0 SET B</li> <li>ASDATA2</li> </ol> |  |  |  |  |  |

| 35                                              | SF_CS_             |          | InOut<br>8mA, SR<br>PU, SMT | 1) Serial Flash Chip Select 2) Trap value in power-on reset : 1 : Serial Flash ATMEL mode 0 : Serial ST/SST mode                                                                                |  |  |  |  |  |

| 36                                              | SF_DO              |          | InOut<br>8mA, SR<br>PD, SMT | Serial Flash Dout                                                                                                                                                                               |  |  |  |  |  |

| Pin | Main  | Alt. | Туре                        | Description                                                                                                                                                                                                                       |

|-----|-------|------|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 37  | SF_DI |      | InOut<br>8mA, SR<br>PU, SMT | 1) Serial Flash Din 2) Trap value in power-on reset : 1 : manufactory test mode 0 : normal operation                                                                                                                              |

| 39  | SF_CK |      | InOut<br>8mA, SR<br>PD, SMT | Serial Flash Clock                                                                                                                                                                                                                |

| 40  | UP1_6 | SCL  | InOut<br>4mA, SR<br>PU, SMT | 1) Microcontroller port 1-6 2) I <sup>2</sup> C clock pin 3) Trap value in power-on reset 1: manufactory test mode 0: normal operation 4) DDC 5) RXD3                                                                             |

| 41  | UP1_7 | SDA  | InOut<br>4mA, SR<br>PU, SMT | <ol> <li>Microcontrolle. port 1-7</li> <li>I<sup>2</sup>C data pin</li> <li>Trap value is power-on reset:         <ol> <li>r rai ufa story test mode</li> <li>normal operation</li> </ol> </li> <li>DDC</li> <li>F.XD3</li> </ol> |

| 44  | PRST_ |      | Input<br>4mA, SR<br>PU, SNT | Power on reset input, active low                                                                                                                                                                                                  |

| 45  | IR    | GPI  | mA, SR<br>SMT               | IR control signal input     GPI                                                                                                                                                                                                   |

|     |       | XOF  | Dram Interface (37)         | (Sorted by position)                                                                                                                                                                                                              |

| 68  | RDo   | 0    | InOut,<br>2mA               | DRAM data 0                                                                                                                                                                                                                       |

| 69  | RD1   |      | InOut<br>2mA                | DRAM data 1                                                                                                                                                                                                                       |

| 70  | RD2   |      | InOut<br>2mA                | DRAM data 2                                                                                                                                                                                                                       |

| 71  | RD3   |      | InOut<br>2mA                | DRAM data 3                                                                                                                                                                                                                       |

| 72  | RD4   |      | InOut<br>2mA                | DRAM data 4                                                                                                                                                                                                                       |

| Pin | Main    | Alt.  | Туре           | Description         |

|-----|---------|-------|----------------|---------------------|

| 70  | DDF     |       | InOut          | DDAM data 5         |

| 73  | RD5     |       | 2mA            | DRAM data 5         |

| 7.4 | DDC     |       | InOut          | DDAM data C         |

| 74  | RD6     |       | 2mA            | DRAM data 6         |

| 75  | DD7     |       | InOut          | DDAM data 7         |

| 75  | RD7     |       | 2mA            | DRAM data 7         |

| 76  | DQM0    |       | InOut          | Data mask 0         |

| 76  | DQIVIO  |       | 2mA, PD        | Data mask 0         |

| 77  | RD15    |       | InOut          | DRAM data 15        |

|     | KD15    |       | 2mA            | DRAW data 15        |

| 78  | RD14    |       | InOut          | DRAM data 14        |

| 76  | ND14    |       | 2mA            | DRAW data 14        |

| 80  | RD13    |       | InOut          | DRAM da ta 13       |

| 80  | KD13    |       | 2mA            | DRAW UZIA 13        |

| 81  | RD12    |       | InOut          | DRAM pata 12        |

| 01  | I KD12  | 2mA   | DIAM Jala 12   |                     |

| 82  | RD11    |       | InOut          | DRAM data 11        |

|     | No II   |       | 2mA            | BIV IVI data 11     |

| 83  | RD10    |       | lr∵)u.<br>2n.A | DRAM data 10        |

| 0.4 | DDO     |       | InOut          | DDAM data 0         |

| 84  | RD9     |       | 2mA            | DRAM data 9         |

| 0.5 | DDo     | .0    | InOut          | DDAM data 0         |

| 85  | RD8     |       | 2mA            | DRAM data 8         |

| 86  | DQN/1   |       | InOut          | Data mask 1         |

| 00  | DQIVI   |       | 2mA, PD        | Data mask i         |

| 0.7 | DCLK    |       | InOut          | Deem sheek          |

| 87  | RCLK    |       | 4mA, PD        | Dram clock          |

|     | 5       |       | InOut          |                     |

| 88  | 88 RA11 |       | 2mA, PD        | DRAM address bit 11 |

|     | DAG     |       | InOut          | DRAM address 0      |

| 89  | RA9     |       | 2mA, PD        | DRAM address 9      |

| 00  | DAG     |       | InOut          | DDAM address 0      |

| 90  | KA8     | RA8 2 | 2mA, PD        | DRAM address 8      |

| Pin        | Main   | Alt.  | Туре    | Description                              |

|------------|--------|-------|---------|------------------------------------------|

| 0.4        | 54     |       | InOut   | DDAM III 7                               |

| 91         | RA7    |       | 2mA, PD | DRAM address 7                           |

| 00         | DAG    |       | InOut   | DDAM address 0                           |

| 93         | RA6    |       | 2mA, PD | DRAM address 6                           |

| 04         | DAE    |       | InOut   | DDAM address 5                           |

| 94         | RA5    |       | 2mA, PD | DRAM address 5                           |

| <b>9</b> 5 | RA4    |       | InOut   | DRAM address 4                           |

| 90         | NA4    |       | 2mA, PD | DIVAINI dudiess 4                        |

| 97         | RWE#   |       | Output  | DRAM Write enable, active ow             |

| 51         | IXVVL# |       | 2mA, PD | DIVAM WITE GRADIE, active low            |

| 99         | CAS#   |       | Output  | DRAM column address st.obe, active low   |

|            | UAO#   |       | 2mA, PD | DIVAM column aut es 5 ti obe, active low |

| 100        | RAS#   |       | Output  | DRAM ro w addr ass strobe, active low    |

| 100        | NAS#   |       | 2mA, PD | Divinite ve daily 33 strobe, active few  |

| 102        | BA0    |       | InOut   | DRAM pank address 0                      |

|            | 27.10  |       | 2mA, PD | S. V. V. Jan. K. dadi 666 6              |

| 103        | BA1    |       | InOut   | DRAM bank address 1                      |

|            | 2, (1  |       | 2mA, PC | 2.0 m. baim addisce                      |

| 104        | RA10   |       | Ir Qui  | DRAM address 10                          |

|            |        |       | ∠mA, PD |                                          |

| 105        | RA0    |       | InOut   | DRAM address 0                           |

|            |        | \_\_\ | 2mA, PD |                                          |

| 106        | RA1    | ×0,   | InOut   | DRAM address 1                           |

|            |        | 2     | 2mA, PD |                                          |

| 107        | RA.    |       | InOut   | DRAM address 2                           |

|            |        |       | 2mA, PD |                                          |

| 108        | RA3    |       | InOut   | DRAM address 3                           |

|            |        |       | 2mA, PD |                                          |

| Pin | Main    | Alt. | Туре             | Description                                                                                                                                                                                       |

|-----|---------|------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 66  | GPIO7   | CKE  | InOut<br>4mA, PD | 1) GPIO 7 2) Dram Clock Enable 3) MS_CLK set A 4) SD_CLK set A 5) HSYN/VSYN input 6) Microcontroller port 1-4 (Internal Pull-Up) 7) Y0 8) HSYN/VSYN output 9) Aclk 10) Asdata1 11) MCDATA 12) CEC |

|     |         |      | GPIC             | O (33)                                                                                                                                                                                            |

| 65  | GPIO8   |      | InOut<br>4mA, PD | 1) GPIO8 2) MS_BS set A 3) SD_CMD set A 4) ASDATA2 5) ACL'( 6) Audio Mule 7) HSYN/VSYN input 8) Mill rocontroller port 1-5 (Internal Pull-Up) Y1 10) HSYN/VSYN Output 11) DDC 12) Y7 SET B        |

| 64  | GPIO9   | xet. | InOut<br>4mA, PD | 1) GPIO9 2) MS_D0 set A 3) SD_D0 set A 4) ASDATA1 5) ABCK 6) RXD1 7) Y2 8) DDC 9) Y6 SET B                                                                                                        |

| 111 | G.PIO10 | HPLG | InOut<br>4mA, PD | 1) GPIO10 2) ASDATA0 3) ALRCK 4) HSYN/VSYN output 5) TXD1 6) DDC                                                                                                                                  |

| Pin | Main   | Alt.   | Туре             | Description                                                                                                                                                                              |

|-----|--------|--------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 42  | GPIO11 |        | InOut<br>4mA, PU | 1) GPIO11 2) SD_CMD set B 3) MS_BS set B 4) Audio Mute 5) HSYN/VSYN output 6) Microcontroller port 3-0 (Internal Pull-Up) 7) RXD1 8) Y4 9) ABCK 10) ASDATA0 11) CEC 12) DDC 13) IPOD_RXD |

| 110 | SPDIF  | GPIO12 | InOut<br>2mA, PD | 1) SPDIF output 2) GPIO12 3) DDC                                                                                                                                                         |

| 63  | GPIO13 |        | InOut<br>4mA, PD | <ol> <li>GPIC 13</li> <li>SD_D0 set B</li> <li>ALF,CK</li> <li>Audio Mute</li> <li>YCLK</li> <li>Y5 SET B</li> </ol>                                                                     |

| 26  | YCLK   |        | InOut<br>4mA, PD | 1) GPIO_YCLK 2) YCLK SET C 3) MS_CLK/SD_CLK SET C                                                                                                                                        |

| 27  | DV_Y0  | y Col  | InOut<br>4mA, PD | 1) GPIO_Y0 2) Y0 SET C 3) MS_BS/SD_CMD SET C                                                                                                                                             |

| 28  | DV_Y1  |        | InOut<br>4mA, PD | 1) GPIO_Y1 2) Y1 SET C 3) MS_D0/SD_D0 SET C                                                                                                                                              |

| 29  | DV_Y2  |        | InOut<br>4mA, PD | 1) GPIO_Y2 2) Y2 SET C 3) SPDATA 4) SPDIFINO                                                                                                                                             |

| Pin | Main  | Alt. | Туре     | Description    |

|-----|-------|------|----------|----------------|

|     |       |      |          | 1) GPIO_Y3     |

| 20  | DV V2 |      | InOut    | 2) Y3 set C    |

| 30  | DV_Y3 |      | 4mA, PD  | 3) SPBCLK      |

|     |       |      |          | 4) SPDIFIN1    |

|     |       |      |          | 1) GPI0_Y4     |

| 31  | DV_Y4 |      | InOut    | 2) Y4 set C    |

| 31  | DV_14 |      | 4mA, PD  | 3) SPLRCK      |

|     |       |      |          | 4) SPDIFIN2    |

|     |       |      |          | 1) GPIO_Y5     |

| 32  | DV_Y5 |      | InOut    | 2) Y5 set C    |

|     | 51_10 |      | 4mA, PD  | 3) VSTB set B  |

|     |       |      |          | 4) SPCLK       |

|     |       |      | InOut    | 1) GPIO_Y6     |

| 33  | DV_Y6 |      | 4mA, PD  | 2) Y6 set c    |

|     |       |      | ,        | 3) SPCLY set B |

| 34  | DV_Y7 |      | InOut    | 1, GF:0_Y7     |

|     | DV_17 |      | 4mA, PD  | 2) Y7 set C    |

|     |       |      |          | 1) GPIO_C0     |

| 48  | DV_C0 |      | Ir. Ou.  | 2) SD_CLK      |

|     |       |      | გ.mA, PD | 3) C0 set B    |

|     |       |      |          | 4) C0 set C    |

|     |       | V    |          | 1) GPIO_C1     |

| 49  | DV_C1 | ×0,  | InOut    | 2) SD_CMD      |

|     |       | 7    | 8mA, PD  | 3) C1 set B    |

|     |       |      |          | 4) C1 set C    |

|     | 10    |      |          | 1) GPIO_C2     |

| 50  | DV_C2 |      | InOut    | 2) SD_D0       |

|     | _     |      | 8mA, PD  | 3) C2 set B    |

|     |       |      |          | 4) C2 set C    |

|     |       |      |          | 1) GPIO_C3     |

| 51  | DV_C3 |      | InOut    | 2) SD_D1       |

|     |       |      | 8mA, PD  | 3) C3 set B    |

|     |       |      |          | 4) C3 set C    |

| Pin | Main      | Alt. | Туре          | Description            |

|-----|-----------|------|---------------|------------------------|

|     |           |      |               | 1) GPIO                |

| 50  | D)/ C4    |      | InOut         | 2) SD_D2               |

| 52  | DV_C4     |      | 8mA, PD       | 3) YCLK set B          |

|     |           |      |               | 4) C4 set C            |

|     |           |      |               | 1) GPIO_C5             |

| 53  | DV_C5     |      | InOut         | 2) SD_D3               |

|     | DV_00     |      | 8mA, PD       | 3) C4 set B            |

|     |           |      |               | 4) C5 set C            |

|     |           |      | InOut         | 1) GPIO_C6             |

| 54  | DV_C6     |      | 4mA, PD       | 2) C5 set B            |

|     |           |      | 1117, 175     | 3) C6 set C            |

|     |           |      | InOut         | 1) GPIO_C7             |

| 55  | DV_C7     |      | 4mA, PD       | 2) C6 set B            |

|     |           |      | 11111, 1, 1 2 | 3) C7 set C            |

|     |           |      |               | 1) GPIC                |

| 56  | SD_MS_CLK |      | InOut         | 2 CU_CLK               |

|     |           |      | 4mA, PD       | 3) MS_CLK              |

|     |           |      | , 26          | 4) C7 set B            |

|     |           |      |               | 1) GPIO                |

| 58  | SD_MS_CMD |      | InQut         | 2) SD_CMD              |

|     |           |      | mA, PD        | 3) MS_BS               |

|     |           |      |               | 4) Y0 set B            |

|     |           | .0   |               | 1) GPIO                |

| 59  | SD_MS_D0  |      | InOut         | 2) SD_D0               |

|     |           | O.   | 4mA, PD       | 3) MS_D0               |

|     | .0        |      |               | 4) Y1 set B            |

|     |           |      |               | 1) GPIO                |

| 60  | SD_MS_D1  |      | InOut         | 2) SD_D1               |

|     |           |      | 4mA, PD       | 3) MS_D1               |

|     |           |      |               | 4) Y2 set B            |

|     |           |      |               | 1) GPIO                |

|     |           |      | InOut         | 2) SD_D2               |

| 61  | SD_MS_D2  |      | 4mA, PD       | 3) MS_D2               |

|     |           |      | 2.10, 1, 1    | 4) Y3 set B            |

|     |           |      |               | 5) 8032 P3.0 (UART RX) |

| Pin | Main     | Alt. | Туре                | Description            |

|-----|----------|------|---------------------|------------------------|

|     |          |      |                     | 1) GPIO                |

|     |          |      | InOut               | 2) SD_D3               |

| 62  | SD_MS_D3 |      |                     | 3) MS_D3               |

|     |          |      | 4mA, PD             | 4) Y4 set B            |

|     |          |      |                     | 5) 8032 P3.0 (UART TX) |

| 130 | GP1029   |      | InOut <b>4mA,PD</b> | 1) GPIO29              |

|     |          |      |                     | 1) GPIO30              |

| 131 | GP1030   |      | In0ut <b>4mA,PU</b> | 2) CP_SDA              |

|     |          |      |                     | 3) ASDATA3 set B       |

|     |          |      |                     | 1) GPIO31              |

| 132 | GPI031   |      | In0ut <b>4mA,PU</b> | 2) CP_SCL              |

|     |          |      |                     | 3) ASDATA3 set C       |

| 133 | GPI032   |      | InOut <b>4mA,PD</b> | 1) GPIO32              |

#### Note:

1. The Main column is the main function, Alt. means alternative function.

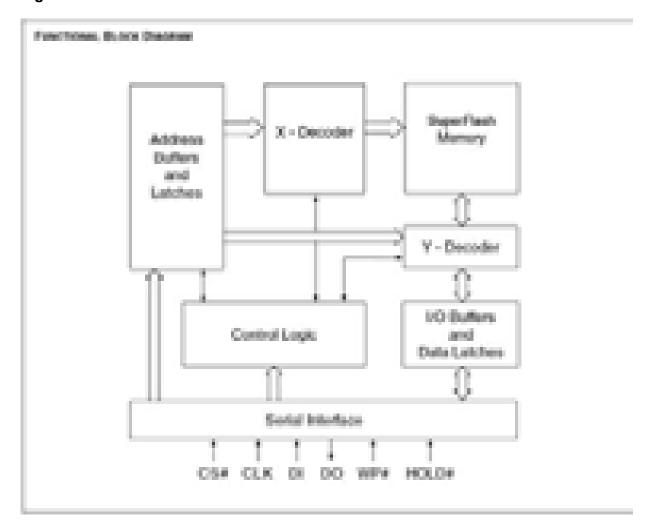

#### 5-5 Functional Block

# 6 Pin Assignment

# 7 Absolute Maximum Ratings

| Symbol                         | Parameters                      | Suggest Value    | Unit |

|--------------------------------|---------------------------------|------------------|------|

| VDD3                           | 3.3V Supply voltage             | -0.2 to 3.6      | V    |

| VDD2                           | 1.2V Supply voltage             | -0.1 to 1.32     | V    |

| VDDA                           | Analog Supply voltage           | -0.2 to 3.6      | V    |

| V <sub>IN</sub> (3.3V)         | Input Voltage (3.3V IO)         | -0.2 to 3.6      | V    |

| V <sub>IN</sub> (5V-tolerance) | Input Voltage (5V-tolerance IO) | -0.3 to 5.5      | V    |

| V <sub>OUT</sub>               | Output Voltage                  | -0.2 to VDD3+0.3 | V    |

| T <sub>STG</sub>               | Storage Temperature             | -45 to 150       | °C   |

# 8 Recommend Operation Condition

| Symbol                 | Parameters                      | Min | Тур | Max | Unit |

|------------------------|---------------------------------|-----|-----|-----|------|

| T <sub>OP</sub>        | Operating Temperature           | 0   |     | 70  | °C   |

| TJ                     | Junction Operation Temp.        | 0   | 25  | 115 | °C   |

| VDD3                   | 3.3V Supply voltage             | 3.1 | 3.3 | 3.6 | V    |

| VDD2                   | 1.2V Supply voltage             | 1.1 | 1.2 | 1.3 | V    |

| VDDA                   | Analog Supply voltage           | 3.1 | 3.3 | 3.6 | V    |

| V <sub>IH</sub> (3.3V) | Input voltage high (3.3\'\'\\') | 2.0 | ı   | 1   | V    |

| V <sub>IL</sub> (3.3V) | Input voltage low (3 3V 10)     | -   | •   | 0.8 | V    |

| I <sub>IH</sub>        | High level input current        |     |     | 10  | UA   |

| I <sub>IL</sub>        | Low leve 'ir, out current       | -10 |     |     | UA   |

| $P_D$                  | Powe, discipation               |     | 1.5 |     | W    |

| P <sub>DOWN</sub>      | F ow r down mode                |     |     | 0.1 | W    |

| fclk                   | put frequency of clock          |     | 27  |     | MHz  |

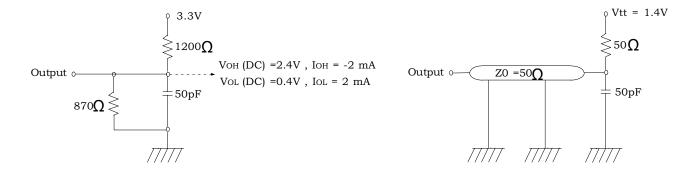

#### 9 Electrical Characteristics

#### 9-1 DC Characteristics

| Symbol                 | Parameters                                                  | Min | Тур | Max | Unit |

|------------------------|-------------------------------------------------------------|-----|-----|-----|------|

| V <sub>OH</sub> (3.3V) | Output voltage high (3.3V IO) (*I <sub>OH</sub> = 2 ~ 16mA) | 2.4 | -   | -   | V    |

| V <sub>OL</sub> (3.3V) | Output voltage low (3.3V IO) (*I <sub>OL</sub> = 2 ~ 16mA)  | -   | -   | 0.4 | V    |

| Rpu                    | Pull-up Resistance                                          | 40  | 75  | 190 | ΚΩ   |

| Rpd                    | Pull-down Resistance                                        | 40  | 75  | 190 | ΚΩ   |

| FOO <sub>OFF</sub>     | Offset voltage between FOO zero output and V <sub>REF</sub> | -50 | 0   | 50  | mV   |

| TRO <sub>OFF</sub>     | Offset voltage between TRO zero output and V <sub>REF</sub> | -40 | 0   | 40  | mV   |

| DMO <sub>OFF</sub>     | Offset voltage between DMO zero output and V <sub>REF</sub> | -30 | 0   | 30  | mV   |

Note \*: The driving current of some IO pad are programmable according to the different application and environment. All setting will be defined according to the F/W progress and test result.

#### 9-2 Built-in Audio-DAC Characteristics

Note \*: All parameters is measured on MediaTek's DVD player reference DVD board, the actual performance depends on different PCB design.

| SYMBOL                                                                                              | PARAMETER                                                                 | MIN. | TYP. | MAX. | UNIT           |

|-----------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|------|------|------|----------------|

| Output swing level:  Vout  Digital i/p level =0 dBFS , ADACVDD =3.3V  (Vout = 1.0 * ADAC (LD / 3.3) |                                                                           | 0.9  | 1.0  | 1.1  | V <sub>P</sub> |

| Ro                                                                                                  | Output imperial cer @ 1kHz                                                |      | 50   | 100  | Ω              |

| R <sub>L_min</sub>                                                                                  | Minim m resister load                                                     | 5    |      |      | K              |

| C <sub>L_max</sub>                                                                                  | Max mu n capacitor load                                                   |      |      | 20   | PF             |

| S/(THD+N)                                                                                           | $\sqrt[3]{(THD+N)} @ 0 dBFS;$<br>$f_{in} = 1kHz$ ; Fs = 48kHz, A-weighted |      | 81   |      | dBr(A)         |

| DR                                                                                                  | Dynamic Range                                                             |      | 82   |      | dBr(A)         |

| SNR                                                                                                 | Signal to noise ratio; A-weighted                                         |      | 92   |      | dBr(A)         |

| Channel<br>Separation                                                                               | Close-talk of Left and Right Channel                                      |      | 81   |      | dB             |

# 9-3 Built-in Audio-ADC Characteristics

| Test signal : 1K Hz sin wave                | Vpp(V)             |                    |

|---------------------------------------------|--------------------|--------------------|

| Max Input (with output THD+N <60 dbfs)      | 3.227V             | 59.9dBFS           |

| DC bias level                               | 1.66V              |                    |

| AKIN DC Level                               | 1.632V             |                    |

| Test signal : 1K Hz sin wave                |                    |                    |

| Input (Vpp)                                 | Output THD+N(dBFs) | filter=A-weighting |

| 3V                                          | -62.27             |                    |

| 2.95                                        | -63.9              |                    |

| 2.9                                         | -65.7              |                    |

| 2.828V                                      | -67.7              |                    |

| 2.75V                                       | -69.9              | 5                  |

| 2.5V                                        | -75.4              |                    |

| 1.5V                                        | -81.9              |                    |

| 0.5V                                        | -84.3              |                    |

| 0V (remove input and short ADVCM with AKIN) | -135.9             |                    |

| Test signal : 2.8 Vpp                       |                    |                    |

| Input frequency:                            | Amp(dBFS)          | filter=none        |

| 1 KHz                                       | -0.422             |                    |

| 4KHz                                        | -0.447             |                    |

| 8khz                                        | -0.518             |                    |

| 16KHz                                       | -0.791             |                    |

| 20KHz                                       | -1.822             |                    |

| 22KHz                                       | -6.848             |                    |

| Dynamic range                               | 283mVpp            |                    |

#### 9-4 Built-in Video-DAC Specifications

Input Codes for Video Application:

|             | NTSC             | NTSC w/setup     | 525_I            | 525_I w/setup    | 525_P            |

|-------------|------------------|------------------|------------------|------------------|------------------|

|             | Programable,     | Programable,     | Programable,     | Programable,     | Programable,     |

| WHITE (235) | Current setting: |

| \           | 3297             | 3297             | 3297             | 3297             | 3290             |

| BLACK (16)  | 960              | 1120             | 960              | 1120             | 1008             |

| PEDESTAL    | 960              | 960              | 960              | 960              | 1008             |

| SYNC TIP    | 64               | 64               | 64               | 64               | 64               |

|             | 525_P w/s | PAL              | 625_I            | 625_P            | RGB              |

|-------------|-----------|------------------|------------------|------------------|------------------|

|             |           | Programable,     | Programable,     | Programable,     | Programable,     |

| WHITE (235) |           | Current setting: | Current setting: | Current setting: | Current setting: |

|             |           | 3290             | 3290             | 3200             | 2282             |

| BLACK (16)  |           | 1008             | 1008             | 1008             | 0                |

| PEDESTAL    |           | 1008             | 1008             | 1008             | -                |

| SYNC TIP    |           | 64               | 64               | 64               | -                |

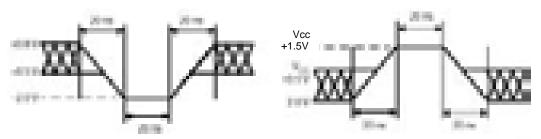

# 9-5 Video Output Voltage Level:

#### High / Low Impedance Mode:

Please contact with FW window for setting High / Love applaance mode.

# 9-6 Video DAC DC Electrical Characteristics

(Operating Free-Air Temperature, AYDD 3.3V, DVDD = 3.3V).

| Analog Output                             |                       | MIN   | TYP   | MAX   | UNIT |

|-------------------------------------------|-----------------------|-------|-------|-------|------|

| Full Scale Output Curre. + CVBS/Y/C/R/G/B | (low impedance mode)  | 34.3  | 34.8  | 35.7  | mA   |

| Full Scale Output Currant CVBS/Y/C/R/G/B  | (high impedance mode) | 8.52  | 8.70  | 8.91  | mA   |

| LSB current CV/bS/://C/R/G/B              | (low impedance mode)  | 33.5  | 34.0  | 34.86 | uA   |

| LSB curren CVBS/Y/C/R/G/B                 | (high impedance mode) | 8.375 | 8.500 | 8.715 | uA   |

| DAC-(2-DAC Mis-Matching                   |                       |       | 1.48  |       | %    |

| Output Compliance                         |                       | 0     |       | 1.38  | V    |

| DAC Output Delay                          |                       |       | 1.5   | 10    | ns   |

| DAC Rise/Fall Time                        |                       |       | 2.1   | 5     |      |

| Voltage Reference                         |                       |       |       |       |      |

| Reference Voltage Output                  |                       |       | 1.22  |       | V    |

| Reference Input Current                   |                       |       | 2.179 |       | MA   |

| Static Performance                        |                       |       |       |       |      |

| DAC Resolution                 |   | 12      |         |        | Bits |  |

|--------------------------------|---|---------|---------|--------|------|--|

| DNL Differential Non-Linearity | + | +/-0.26 | +/-0.48 | +/-0.6 | LSB  |  |

| INL Integral Non-Linearity     | + | +/-0.40 | +/-0.67 | */-0.9 | LSB  |  |

| Dynamic Performance            |   |         |         |        |      |  |

| Differential Gain              |   |         | 0.77    | 1.5    | %    |  |

| Differential Phase             |   |         | 0.23    | 1.5    |      |  |

| S/N Ratio                      |   | 70      |         | 1.     | dB   |  |

| Power Supply                   |   |         |         |        |      |  |

| Supply Voltage                 |   | 3.0     | 3.0     | 3.6    | V    |  |

# 9-7 RF specification

| Item                              | Designator           | Conditions                      | Min  | Тур  | Max  | Unit  |

|-----------------------------------|----------------------|---------------------------------|------|------|------|-------|

| 3.3V POWER                        |                      | KO.                             | 3.00 | 3.30 | 3.60 | Volts |

| 5 B W                             |                      | Enable power down               | 10   | 27   | 50   | mA    |

| Power Down Mode                   |                      | Chip Reset                      | 90   | 151  | 200  | mA    |